Tachyum poursuit Cadence pour $211 millions pour une IP défaillante

Le concepteur de processeurs européen Tachyum basé à Bratislava et à Las Vegas, USA, poursuit Cadence Design Systems aux États-Unis pour 211 millions de dollars concernant des blocs IP de mémoire et d’interface défaillants.

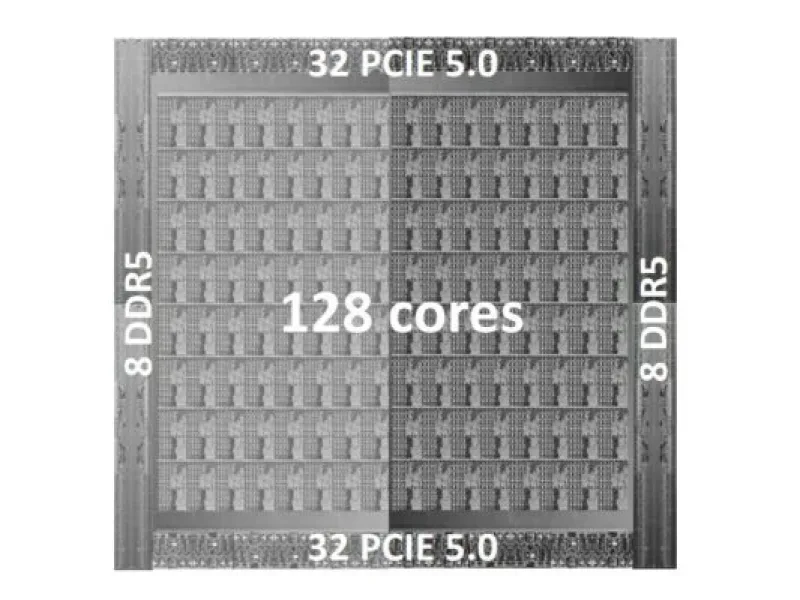

Tachyum développe un processeur universel capable de gérer les opérations d’un CPU, d’un GPU et d’un accélérateur d’IA dans la même puce. La puce comporte 128 cœurs et est destinée aux centres de données et aux superordinateurs, en utilisant 64 interfaces PCI Express (PCIe) 5.0 et 16 interfaces mémoire DDR5.

Autres articles Tachyum

-

$400 millions pour un centre de conception RISC-V à Barcelone

- Tachyum plans 3nm Universal processor

- Tachyum teams for German supercomputer

- Slovakia aims to build world’s fastest AI supercomputer

Le projet de conception Prodigy aurait dû être finalisé et envoyé en production l’année dernière sur un process de 5 nm, mais a été considérablement retardé car il y avait des problèmes avec les blocs IP d’interface mémoire PCIe et DDR5. « Nous avons acheté l’IP pour la mémoire DDR5 et PCIe et le fournisseur avait un problème », a déclaré Radoslav Danilak, fondateur et PDG de Tachyum, à eeNews Europe précédemment.

«Nous avons remplacé cela par Rambus et AlphaWave et un autre pour la DDR5. Ce fut une mauvaise surprise, mais la bonne nouvelle est que la nouvelle IP est intégrée et prête maintenant. »

Dans un recours judiciaire déposé à Santa Clara, en Californie, le fournisseur de ces blocs est identifié comme étant Cadence. Cadence a refusé de commenter. « Cadence ne commente pas les procédures judiciaires en cours », a-t-il déclaré.

L’accord était important, les contrats avec Cadence totalisant un quart des fonds que Tachyum a levés à ce jour, soit 42 millions de dollars selon Crunchbase. Bien que l’accord ait pu valoir jusqu’à 10 millions de dollars, il semble qu’environ 5 millions de dollars aient été payés, bien que cela soit expurgé dans les documents judiciaires.

« Pendant près de deux ans, Tachyum a essayé de travailler avec Cadence pour trouver des solutions à ces problèmes malgré les retards et les frustrations persistants et généralisés du projet », indique le recours. « Le lourd investissement de Tachyum dans la relation avec Cadence, à la fois financièrement et technologiquement, signifiait qu’il ne serait pas simple de passer à d’autres fournisseurs et prestataires de services. En fin de compte, cependant, Tachyum a déterminé qu’il n’avait pas le choix.

Une partie du problème était le verrouillage lié à l’utilisation des outils de conception Cadence et le temps nécessaire pour passer aux outils d’autres fournisseurs.

Rambus fournit désormais son IP PCI Express (PCIe) 5.0, tandis que la société britannique Alphawave fournit son PHY AlphaCORE Long-Reach (LR) Multi-Standard-Serdes (MSS) avec des vitesses allant jusqu’à 112 Gbps.

Tachyum demande le remboursement de l’argent dépensé pour le contrat, qui peut atteindre 10 millions de dollars, avec au moins 206 millions de dollars supplémentaires « en augmentation des dépenses et en manque à gagner causés par la conduite fautive de Cadence », a-t-il déclaré.

Ce manque à gagner vient de la non participation aux projets tels que le MareNostrum 5 développé par le Barcelona Supercomputing Center (BSC) en Espagne, qui aurait valu 151 millions d’euros. Le retard signifiait également un manque de commandes d’au moins 20 millions de dollars, indique la plainte.

Les fabricants de puces soutiennent CXL 3.0 pour l’interconnexion de mémoire des centres de données

Chip makers back CXL 3.0 for data centre memory interconnect

La conception du Prodigy 2 de prochaine génération sera construite sur un process de 3 nm et ajoutera l’interface mémoire CXL et les voies PCIe 6.0 des mêmes fournisseurs IP et augmentera le nombre de cœurs. Le plan est de pouvoir fournir des échantillons de cette puce en 2024.

www.tachyum.com; www.cadence.com

Autres articles sur ECI News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News