TSMC cherche à normaliser les protocoles de chiplets 3D

TSMC cherche à développer un format de données standard pour les conceptions de chiplets qui serait utilisé par tous les fournisseurs d’outils de conception, d’assemblage et de test de l’EDA.

Cette initiative s’inscrit dans le cadre de l’adoption de la technologie 3D Blox pour la conception de chiplets sur le processus CoWoS de TSMC. L’objectif est de fournir des données communes pour les chiplets provenant de différents fournisseurs de silicium, de fabricants de substrats et de circuits imprimés et des sociétés d’assemblage et de test de l’OSAT.

« Aujourd’hui, la plupart des puces, à l’exception des mémoires, proviennent de TSMC, mais l’objectif est de les mélanger et de les assortir, ce qui n’est pas encore le cas, mais nous essayons d’y parvenir », a déclaré Dan Kochpatcharin, responsable de l’infrastructure de conception chez TSMC.

« Nous avons passé l’année dernière à travailler avec eux pour les aider à comprendre que la collaboration est nécessaire à la réalisation de l’IC 3D », a-t-il déclaré. « Nous avons besoin que les fabricants de substrats et de circuits imprimés se parlent pour créer un fichier de substrat qui puisse être lu par tous les fournisseurs d’EDA – nous y travaillons et nous en sommes à 80 % », a-t-il déclaré. « L’OSAT s’occupe également de l’acheminement du substrat et nous devons donc nous assurer qu’ils utilisent les mêmes outils. L’intégration de tout cela change la donne ».

- Synopsys et Cadence étendent la prise en charge de 3D Blox 2.0 aux conceptions chiplet

- Keysight rejoint l’alliance TSMC pour stimuler l’écosystème des circuits intégrés 3D

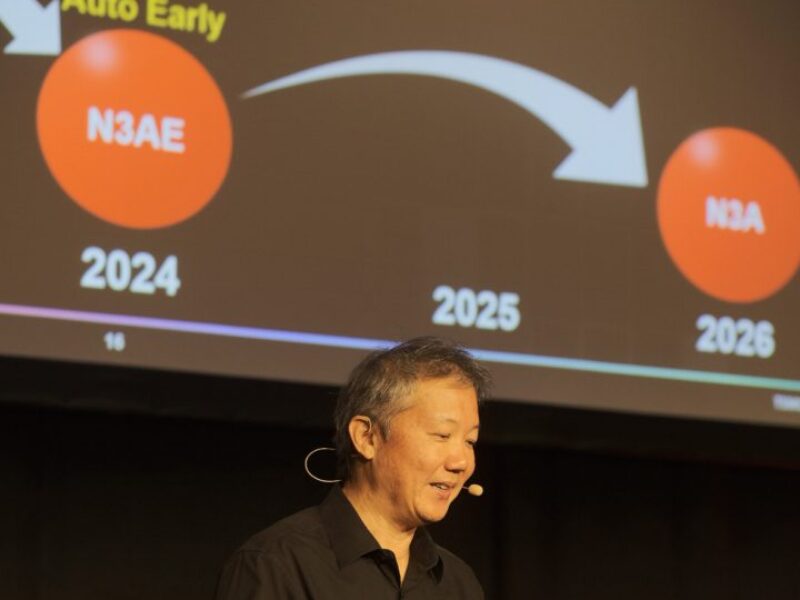

- Plate-forme unifiée de chiplets à 3 nm avec UCIe IP

La dernière version du protocole 3D Blox est déjà utilisée par Synopsys et Cadence. Les outils PCB XSI/XPD de Siemens EDA et Ansys le prennent en charge pour l’analyse et la conception de PCB et de substrats.

« Nous avons donc mis le texte en ligne et dit aux partenaires de l’AED qu’ils pouvaient le communiquer à n’importe qui », a-t-il déclaré. « Nous voulions un moyen unique de modulariser ce système, de la connectivité au câblage et à l’empilage. La faisabilité doit être précoce – lorsque vous avez 10 millions de bumps bosses, il est important de savoir comment elles s’alignent, car les outils pour circuits imprimés ne gèrent pas des millions de bumps ».

La version 2.0 ajoute les matrices empilées aux outils de détourage. « Il ne s’agit pas seulement d’un empilement physique, mais aussi d’une multitude d’aspects multi-physiques, avec différentes dilatations thermiques et de puissance, et ce n’est pas si simple avec les vias de silicium traversants et les différents choix d’intercalaires », a-t-il déclaré.

La prochaine étape consistera à mettre au point un format unique pour tester les substrats. Ceci est important car la taille du substrat passera de la technologie actuelle du processus COWoS-S, qui est 3,5 fois la taille du plus grand réticule, à CoWoS -R et -L, qui sera jusqu’à 6 fois la taille du réticule (13 x 13 cm). « Vous avez toujours besoin de quelque chose entre les deux, mais cela ne saurait tarder », a-t-il déclaré.

Un format unique pour les tests est également nécessaire.

« Il faut un format unique pour les testeurs et les outils DFT, de sorte que nous puissions faciliter le test pour un testeur, les emplacements de sondage des broches. La méthodologie est alors du côté du client », a-t-il déclaré.

- Siemens EDA et SPIL s’associent pour développer des chiplets en éventail

- Siemens et ASE prolongent leur accord sur l’emballage 3D

TSMC collabore avec ASE et SPIL dans le cadre de la plateforme d’innovation ouverte (OIP) afin de poursuivre le développement de la technologie des circuits intégrés en 3D et travaille sur des projets de chiplets automobiles. « Nous avons près de 100 partenaires dans l’OIP », a-t-il déclaré. « Nous n’acceptons pas n’importe qui – s’ils nous rejoignent, nous nous assurons qu’ils respectent le calendrier de la technologie afin qu’elle soit prête pour le client ».

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News