Outil « Bon par construction » pour l’alimentation interne des puces

Siemens Digital Industries Software a mis au point un outil de conception de la puissance des puces qui permet d’améliorer la conception et la fiabilité grâce à une approche « correcte par construction » jusqu’à 2 nm.

Calibre DesignEnhancer met automatiquement en œuvre les modifications de la disposition de la conception pour le routage de l’alimentation, la chute de tension IR et l’électromigration beaucoup plus tôt dans le processus de conception et de vérification des circuits intégrés sur les conceptions de 130 nm à 2 nm.

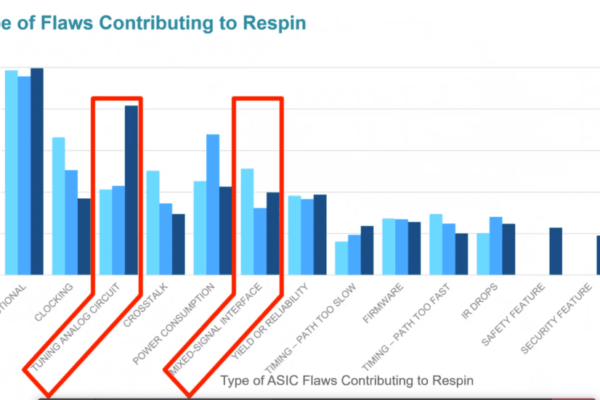

Avant de procéder à la vérification physique de la conception d’un circuit intégré, les ingénieurs s’appuient traditionnellement sur des outils P&R tiers pour intégrer les optimisations de la conception pour la fabrication (DFM), ce qui nécessite souvent de nombreuses itérations fastidieuses avant de converger vers une version propre pour les vérifications des règles de conception. Le nouvel outil vise à raccourcir ce processus de nettoyage DRC et à réduire les problèmes EM/IR lors de la préparation d’un schéma pour la vérification physique.

- Siemens EDA et SPIL s’associent pour développer des chiplets en éventail

- Sondrel prolonge l’accord EDA avec Siemens

- Les équipes EDA de Siemens pour les conceptions en 3D et les chiplets

L’outil Calibre DesignEnhancer propose actuellement trois modèles d’utilisation :

La modification des via analyse automatiquement les schémas et insère jusqu’à plus d’un million de vias Calibre-clean corrects par construction afin de réduire l’impact de la résistance des vias sur l’EM/IR et la fiabilité. Parce que ces modifications sont basées sur une compréhension approfondie des règles de conception de l’agencement et du signoff, l’insertion de via peut aider les clients à atteindre leurs objectifs en matière de puissance sans avoir d’impact sur les performances ou les mesures de surface.

L’amélioration de l’alimentation/masse analyse automatiquement les tracés et insère des vias et des interconnexions propres au nmDRC de Calibre dans les pistes ouvertes pour créer des parcours parallèles qui peuvent réduire la résistance sur les structures d’alimentation/masse et réduire les problèmes d’IR et d’EM associés au réseau électrique. Les clients qui utilisent l’outil DesignEnhancer de Calibre ont obtenu des réductions allant jusqu’à 90 % des problèmes de chute d’IR.

L’insertion de cellules de remplissage optimise l’insertion du condensateur de découplage (DCAP) et des cellules de remplissage nécessaires à la préparation de la vérification physique. Il remplace les processus traditionnels d’insertion de cellules de remplissage P&R, ce qui permet d’obtenir des résultats de meilleure qualité et des temps d’exécution jusqu’à 10 fois plus rapides.

La solution Calibre DesignEnhancer s’est avérée déterminante dans nos efforts continus pour « déplacer vers la gauche » nos processus de conception de circuits intégrés, par exemple en abordant et en résolvant les problèmes de résistance hors spécification et de chute IR », a déclaré Pier Luigi Rolandi, directeur principal de la R&D chez STMicroelectronics.

« Dans l’environnement actuel de conception de circuits intégrés, les équipes d’ingénieurs travaillant sur des nœuds avancés s’efforcent d’optimiser les schémas pour la fabrication et la performance dans les limites de la zone donnée et des contraintes de temps du projet dans lesquelles ils doivent travailler », a déclaré Michael White, directeur principal de la gestion des produits de vérification physique, Calibre Design Solutions, Siemens Digital Industries Software. « En utilisant le logiciel Calibre DesignEnhancer, les concepteurs peuvent utiliser la vitesse et la précision du traitement polygonal de Calibre plus tôt dans le cycle de conception, ce qui permet d’éviter les surprises à la fin du cycle de conception.

La solution Calibre DesignEnhancer utilise une technologie éprouvée, des moteurs et des jeux de règles qualifiés de Calibre, qui peuvent tous aider les clients à générer des résultats qui sont corrects par construction, propres à Calibre DRC et prêts pour la vérification du sign-off. Il peut lire OASIS, GDS et LEF/DEF comme fichiers d’entrée et produire des modifications de disposition dans n’importe quelle combinaison de fichiers OASIS, GDS ou DEF incrémentiels, ce qui aide les équipes de conception à rétro-annoter les modifications apportées par le logiciel Calibre DesignEnhancer à la base de données de conception pour l’analyse de la puissance et de la synchronisation à l’aide d’outils couramment utilisés pour une analyse plus poussée plus tôt dans le cycle de vie de la création de la conception.

L’outil Calibre DesignEnhancer fait partie de la plate-forme Calibre nmPlatform pour la vérification physique des circuits intégrés et s’intègre à tous les principaux environnements de conception et de mise en œuvre en utilisant les normes d’interface de l’industrie, fournissant un environnement convivial qui nécessite une formation et une configuration minimales.

Les kits Calibre DesignEnhancer sont disponibles dès à présent pour toutes les principales fonderies et prennent en charge les conceptions de 130 nm à 2 nm, en fonction du modèle d’utilisation et de la technologie.

https://eda.sw.siemens.com/en-US/ic/calibre-design/design-for-manufacturing/designenhancer/

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News