Le CEA-Leti trace la voie vers une informatique quantique utilisant le FDSOI

Les qubits à spin sur silicium représentent l’une des voies les plus prometteuses pour réaliser l’informatique quantique en pratique, et de nouvelles recherches sur les procédures de test paramétriques à température ambiante soutiennent à la fois leur fort potentiel de performance et les opportunités de faciliter leur transition vers la fabrication en utilisant des processus et des matériaux bien caractérisés du secteur des semiconducteurs.

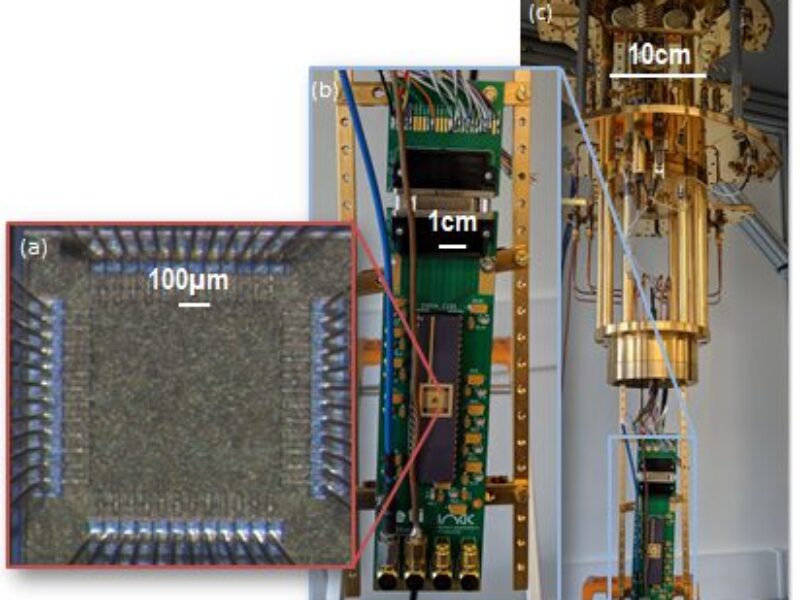

Dans une communication invitée au Symposium IEEE VLSI sur la technologie et les circuits 2022, des chercheurs du CEA-Leti, de l’Université Grenoble Alpes, du CNRS Institut Néel et du CEA-Irig ont partagé une nouvelle chaîne de caractérisation en trois étapes pour les matrices linéaires de « Dots » quantiques (QD) sur silicium fabriqué sur un matériau entièrement appauvri de silicium sur isolant (FDSOI).

L’équipe a également proposé plusieurs propositions de méthodologies et de mesures pouvant accélérer les cycles d’apprentissage à 300K, tout en générant des données statistiques sur les performances attendues des composants à des températures cryogéniques.

Autres articles quantum dot

-

Siemens fait équipe avec Pasqal pour l’EDA quantique

- Créer un leader de l’informatique quantique en Europe

L’approche en trois étapes maximise l’efficacité des tests à température plus élevée dans le cadre de la volonté plus large de rendre les dispositifs QD en silicium manufacturables, en permettant aux développeurs de détecter et d’analyser les problèmes au point le plus précoce et le plus simple. « C’est un pas important vers l’industrialisation », a déclaré le Dr Maud Vinet, directrice du programme d’informatique quantique au CEA-Leti.

L’étape initiale de caractérisation au niveau du wafer à température ambiante qui utilise des protocoles de test de type transistor pour recueillir des données en quelques heures, est suivie d’une étape de caractérisation QD au niveau du wafer plus longue à moins de 2 degrés K, et une étape de manipulation de niveau qubit de la puce (qui peut prendre des jours par composant) à moins de 100 mK.

L’équipe de recherche a utilisé le processus pour évaluer plusieurs considérations liées à la production de réseaux QD intégrés et faire des recommandations pour les résoudre.

Une telle considération concerne l’utilisation proposée de réseaux linéaires de QD à grille flottante pour fonctionner d’une manière similaire à un transistor standard à grille unique. Les chercheurs ont découvert que les portes internes de ces réseaux offrent des performances de pointe constantes sur la tension de seuil (Vth) et la pente sous le seuil (SS), mais que les portes externes présentent une plus grande variabilité. Les chercheurs proposent de traiter ces particularités d’effet de bord (qui peuvent être causées par des facteurs tels que la fluctuation aléatoire du dopant) en utilisant les portes extérieures comme portes d’accès plutôt que pour le confinement des QD.

Alors que la conception à porte divisée explorée pour les réseaux QD linéaires offre plusieurs avantages fonctionnels, sa mise en œuvre réussie nécessitera un contrôle de superposition très strict sur une étape de lithographie spécifique pour obtenir une bonne symétrie, nécessaire pour des performances constantes.

Une troisième recommandation est axée sur le problème des « Dots » parasites dans la couche qubit – une source majeure de perte de rendement dans les matrices QD silicium. Des « Dots » parasites peuvent être détectés lors des tests cryogéniques, mais révéler la défectuosité inter-portes qui les provoque plus tôt dans la chaîne de caractérisation (comme lors des tests 300K) accélérerait considérablement le cycle d’apprentissage.

Bien que les tests paramétriques standard de transistor ne soient pas adaptés à la tâche, les chercheurs ont développé une technique de balayage de tension à 300K capable de surveiller l’effet de dépistage que la défectuosité inter-porte a sur la polarisation de la porte d’échange.

Other quantum computing articles

- D-Wave steps up battle for quantum computers

- First room-temperature quantum computer in supercomputing centre

- EU Foresight report highlights semiconductors, quantum and space

- Sweden to build its own quantum computer

- Open design for large scale quantum computer

L’un des principaux avantages du matériau FDSOI utilisé dans les efforts du groupe, a déclaré Vinet, est le fait que les portes arrière peuvent être utilisées pour éloigner les charges des interfaces. Les portes arrière sont généralement fabriquées à l’aide d’une implantation de dopants, qui a le potentiel d’introduire des défauts ou des dopants parasites dans la couche qubit. Une approche de fabrication alternative, utilisant une électrode de grille arrière métallique de type TSV, serait un moyen d’atténuer cet inconvénient tout en permettant une rétropolarisation, a-t-elle ajouté.

« Ces résultats de recherche représentent une étape importante vers la résolution des problèmes plus larges d’intégration des qubits de spin sur silicium dont nous avons discuté lors de la conférence IEDM de décembre dernier « , a déclaré Heimanu Niebojewski, ingénieur en chef des dispositifs au CEA-Leti. « C’est un signe très encourageant de la maturation de la technologie. »

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News