Axelera lance Metis, une carte edge pour l’IA en mémoire

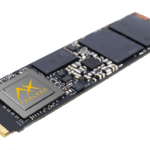

La startup néerlandaise Axelera lance une carte PCI Express pour sa puce d’accélération Metis et prévoit de proposer une carte plus petite au format M.2 le mois prochain.

« Il s’agit d’un véritable produit européen avec des performances et une efficacité de pointe », explique Fabrizio Del Maffeo, PDG et cofondateur d’Axelera, à eeNews Europe.

La carte PCIe à $149 est un élément clé de la stratégie visant à fournir une vision artificielle pour les applications de pointe.

« La livraison d’une puce n’est pas une solution évolutive », a déclaré M. Fabrizio. « Nvidia ne vend pas juste une puce. Nous voulons que le client ait une expérience d’intégration fluide et rapide, c’est pourquoi, dès le premier jour, nous avons dit que nous allions concevoir une carte d’accélération. Ainsi, après seulement deux ans, nous avons fait passer l’entreprise à 140 personnes et nous avons mis sur le marché deux puces avec des dizaines de clients. Il s’agit d’une étape très importante, car il est essentiel que le matériel soit mis entre les mains des clients.

« Nous ne sommes pas seulement une société de semiconducteurs, nous possédons de la propriété intellectuelle dans le domaine du calcul en mémoire et du RISC-V, mais aussi au niveau des algorithmes avec la quantification, l’optimisation du réseau et la recherche d’une architecture de réseau afin d’offrir des performances plus élevées avec une latence et un temps d’apprentissage plus faibles ».

La puce Metis est la deuxième puce de la société et utilise une architecture de calcul numérique en mémoire pour réduire la consommation d’énergie, atteignant 214 TOPS avec une enveloppe de puissance de 3 à 16 W pour les applications embarquées. Elle est fabriquée sur le process TSMC 12nm.

- Plate-forme RISC-V AI pour la vision périphérique

- Le tour de table de la série A passe à 50 millions de dollars

- 27 millions de dollars pour l’informatique en mémoire à la périphérie

« Thetis a été la puce de test pour valider le moteur de calcul numérique en mémoire qui se trouve au cœur de l’accélérateur », a déclaré Paul Neil, vice-président de la gestion des produits chez Axelera. « Nous avons ensuite construit un SoC complet autour de quatre instances du moteur d’accélération de l’IA, avec le moteur matriciel et un moteur scalaire, et c’est Metis. Chaque cœur est contrôlé par un cœur RISC-V dans une architecture de flux de données ».

La puce est dotée d’une mémoire cache L2 de 32 millions de pixels permettant d’exécuter des frameworks d’intelligence artificielle en mémoire. « En eux-mêmes, les cœurs sont capables de traiter une grande variété de framworks d’intelligence artificielle », a déclaré M. Neil. « Le cache L2 de 32M permet aux cœurs de communiquer avec des réseaux indépendants sur chaque cœur, ou avec plusieurs cœurs utilisant le même réseau ou le pipelining temporel et spatial. »

Il existe une interface mémoire LPDDR4x « pour les modèles plus importants qui dépassent les 32M », a déclaré Neil.

La carte PCIe 3.0 est intégrée dans un serveur de vision périphérique d’Advantech, et une carte à quatre puces est prévue pour l’année prochaine, ce qui permettrait d’atteindre 856 TOPS.

De même qu’il ne suffit pas de vendre une puce, le logiciel est essentiel pour être adopté par des ingénieurs qui ne sont pas des spécialistes des données. L’objectif est que la puce Metis soit un accélérateur à côté d’un processeur hôte.

« Nous disposons d’un kit de développement logiciel (SDK) complet qui va de pair avec les produits du système et qui comporte un certain nombre de composants », a déclaré Neil. Un compilateur optimisant TVM appelé Voyager compile un réseau neuronal d’IA sur la puce, tandis que le modèle Axelera zoo fait correspondre les frameworks à l’architecture de calcul en mémoire », a déclaré Neil.

« Beaucoup de nos clients ont des pipelines de vision bien développés qui tournent sur l’hôte et ils veulent se lier au runtime et exécuter l’accélération sur la carte », a-t-il déclaré.

« Nous disposons d’un développement à code réduit. Les ingénieurs peuvent importer des modèles pré-entraînés en utilisant le langage YAML pour prototyper et développer avec tous les outils, ce qui donne un point d’entrée léger dans la chaîne d’outils. Cette approche à code réduit sera complétée par un environnement de composition graphique sans code basé sur le cloud d’ici la fin du premier trimestre 2024. »

La chaîne d’outils a été conçue pour répondre aux besoins de toutes les catégories d’utilisateurs, explique Neil, depuis les innovateurs et les utilisateurs précoces dotés de nombreuses compétences en matière d’apprentissage automatique et capables d’exploiter pleinement les performances du compilateur Voyager jusqu’aux ingénieurs en logiciels embarqués qui souhaitent résoudre un problème commercial.

« Avec la première phase du programme d’accès anticipé, nous démontrons notre capacité à optimiser les modèles.

Framework du transformer

De nombreux développeurs de puces d’IA de pointe portent les frameworks de transformation sur leurs architectures. C’est également un point sur lequel Axelera se penche, déclare Neil.

« L’IA pour la vision par ordinateur est une technologie bien comprise et mature », a déclaré Neil. « Ce que nous observons pour les transformateurs de vision, c’est typiquement un framework hybride avec des éléments de transformateur de vision, de sorte que le soutien futur se fera au niveau des primitives pour prendre en charge une large gamme de primitives de transformateur de façon native dans le matériel.

L’entreprise travaille également avec deux partenaires d’intégration, Advantech et Carbon Systems. « Nous vendons directement ou ils vendent directement », a déclaré FDM. « Nous n’avons pas l’intention de nous adresser à l’utilisateur final, mais d’aider l’intégrateur et le partenaire à développer des logiciels spécifiques pour des applications, qu’il s’agisse de systèmes de surveillance ou d’inspection des cultures.

Feuille de route pour le silicium

« Notre conception est un processus numérique à 12 nm, ce qui nous permet de profiter très facilement des améliorations en termes de performances et de coûts, il s’agit d’une solution de volume », a déclaré Neil. « Il y a plusieurs façons d’explorer l’espace de l’architecture. Il est conçu pour le CNN pour la vision, et il y a un certain nombre de vecteurs que nous pouvons suivre – l’évolutivité de l’architecture, l’innovation de l’arche, l’évolutivité de l’appareil et l’évolutivité du processus ».

« Mais nous sommes un agrégateur, pas un intégrateur. Nous sommes un nœud dans le réseau, nous prenons des flux multiples et nous les traitons avec un hôte qui peut être mis à l’échelle et approvisionné pour l’application.

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News