Des chercheurs d’ARM et d’IBM ont développé une puce de calcul analogique en mémoire de 14 nm pour l’apprentissage automatiqueune faible consommation toujours actif.

Ces tâches de perception permanentes dans les applications IoT, appelées TinyML, nécessitent une efficacité énergétique très élevée. Le calcul en mémoire (CiM) analogique utilisant une mémoire non volatile (NVM) promet une efficacité énergétique élevée et un stockage de modèle sur puce autonome.

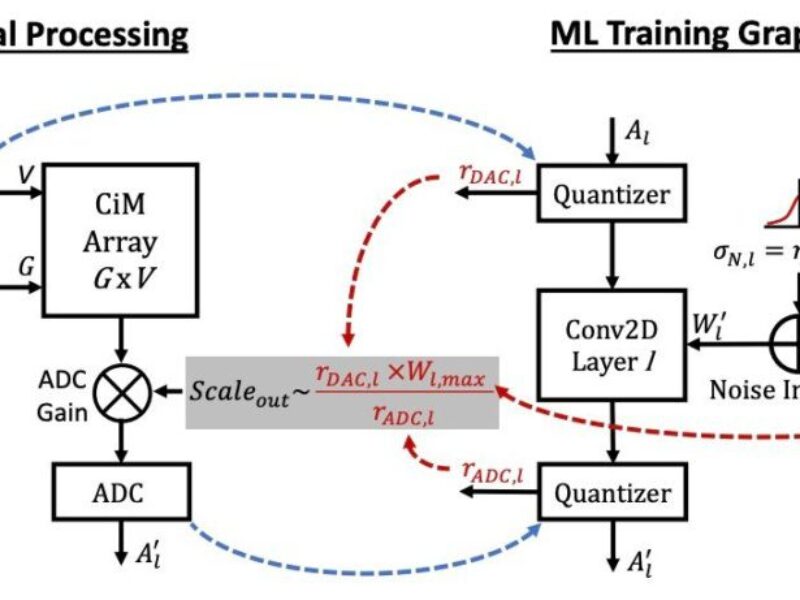

Cependant, le CiM analogique introduit de nouveaux défis pratiques, notamment la dérive de conductance, le bruit de lecture/écriture, le gain fixe du convertisseur analogique-numérique (ADC), etc. Ceux-ci doivent être résolus pour obtenir des modèles pouvant être déployés sur le CiM analogique avec une perte de précision acceptable. .

Des chercheurs d’ARM et d’IBM Research Zurich ont examiné les modèles TinyML pour les tâches populaires de veille (toujours actives) de repérage de mots clés (KWS, Keyword spotting ) et de mots de réveil visuels (VWW, Visual Wake Words). Les architectures modèles sont spécialement conçues pour le CiM analogique et détaillent une méthodologie d’apprentissage complète, pour conserver la précision face aux problèmes de l’analogique et aux convertisseurs de données de faible précision au moment de l’inférence.

-

STMicro prépare une puce IA avec calcul analogique en mémoire

-

Le Leti dévoile un capteur d’image de reconnaissance faciale

-

1400 coeurs RISC-V pour l’apprentissage automatique sur une puce

- First In Memory Computing chip for GDDR6

Ils ont développé un accélérateur CiM analogique utilisant une mémoire à changement de phase (PCM) à surface minimale programmable appelé AON-CiM sur une technologie de process de 14 nm. Cette technologie utilise une série de couches qui élimine le coût des interconnexions complexes associées à une conception entièrement en pipeline.

L’évaluation des réseaux analogiques sur un simulateur calibré, ainsi que sur du matériel réel, a montré que la dégradation de la précision est limitée à 0,8 %/1,2 % après 24 heures de dérive PCM (8 bits). L’exécution des réseaux sur l’accélérateur AON-CiM 14 nm démontre 8,55/26,55/56,67 et 4,34/12,64/25,2 TOPS/W pour le repérage de mots clés (KWS) et les mots d’éveil visuels (VWW) avec des activations 8/6/4 bits respectivement.

« Les techniques analogiques de calcul en mémoire peuvent convenir aux tâches de TinyML de perception à ultra-basse consommation, telles que la détection de mots clés et les mots d’éveil visuels dans les applications informatiques de pointe », a déclaré Paul Whatmough, responsable de la recherche sur l’apprentissage automatique chez ARM Research aux États-Unis.

« Notre article, en collaboration avec l’incroyable équipe d’IBM Research Zurich, donne une plongée approfondie sur la co-conception du modèle d’apprentissage automatique et du matériel analogique, couvrant la conception de modèles et l’apprentissage sur du hardware bruyant, ainsi que le hardware compact efficace (et pratique) pour le calcul en couche-série en mémoire. Nous testons même les modèles sur du hardware réel.

https://ieeexplore.ieee.org/abstract/document/9855854

Lire aussi:

Silina courbe les capteurs d’image à échelle industrielle

Related analog in-memory compute articles

- ST hints at analog in-memory computing chip

- Analog-in-memory AI processor startup uses memristors

- Axelera shows DIANA analog in-memory computing chip

- 48 core neuromorphic AI chip uses resistive memory

- 1400 RISC-V cores for on-chip machine learning

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News