Xilinx prépare une architecture révolutionaire à 7nm

Lors d’un pré-lancement à Londres, le PDG récemment élu Victor Peng a justifié le besoin de la nouvelle architecture comme un moyen de contourner l’obsolecense de la loi de Moore, et considère l’ACAP comme la mère de tous les futurs ASIC.

Ce n’est pas que nous ne sachions pas comment aller au nœud suivant, mais l’économie de la loi de Moore a cessé de fonctionner: obtenir de meilleures performances ou des appareils plus rapides pour toujours moins cher n’est plus vrai », a déclaré le PDG. Cela laisse supposer que pour les concepteurs d’ASIC, il devient de plus en plus difficile de trouver les volumes qui justifieraient la valeur fixe d’un ASIC, sans possibilité de l’optimiser pour un large éventail d’applications.

« La vitesse de l’innovation est plus rapide que les cycles de conception de silicium, et que pouvons-nous faire pour relever ce défi? » demande Peng au public, en soulignant le besoin de puces adaptables.

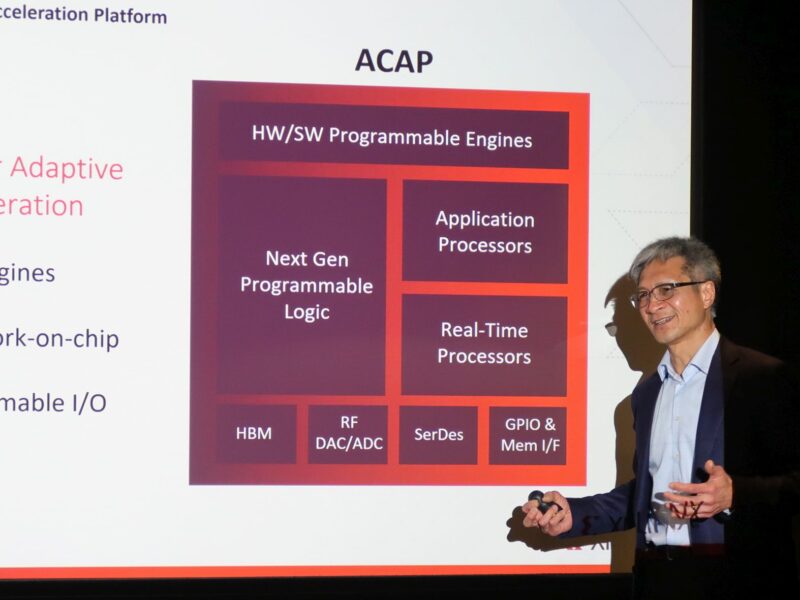

L’ACAP a été présenté comme une rupture technologique majeure pour l’industrie, et le plus important accomplissement en ingénierie de Xilinx depuis l’invention du FPGA, rien de moins. À la base, l’ACAP dispose d’une nouvelle génération de structures FPGA avec mémoire distribuée et blocs DSP programmables par hardware, un SoC multicœur et un ou plusieurs moteurs de calcul programmables, mais aussi adaptables par hardware, tous connectés via un réseau sur puce (NoC ). Peng est cependant resté évasif en ce qui concerne l’assemblege réel des structure. « La façon dont nous créons le « bitstream » (flux binaire) est complètement différent, et le NoC permet un contrôle de flux supérieur au GHz », a déclaré le PDG lors d’un entretien avec eeNews Europe. ( publication accociée de ECI)

L’ACAP dispose également de fonctionnalités d’E / S programmables hautement intégrées, allant des contrôleurs de mémoire programmables matériels intégrés, de la technologie SerDes avancée et des ADC / DAC de pointe à la mémoire HBM (High Bandwidth Memory) intégrée selon la variante du composant. Ce qui le rend adaptatif, c’est qu’il peut être modifié au niveau du hardware pour s’adapter aux besoins d’une large gamme d’applications et de charges de travail, de façon dynamique pendant le fonctionnement.

Celà permet de fournir des niveaux de performance supérieurs d’une magnitute aux CPU actuels, tout en étant adaptable à plus de cas d’utilisation que les GPU ou les ASIC. Mais n’avons-nous pas déjà entendu cette histoire de reconfigurabilité à la volée maintes fois? donc que-ce-qu’il y a de différent cette fois-ci? L’ACAP s’adapte à de multiples charges de travail sur le même surface de silicium, avec des moteurs reconfigurables dans un nouveau type de structures (lui-même reconfigurable?)

Est-ce que Xilinx pourrait emprunter certains des nouveaux éléments de structures de la startup FPGA Efinix? La startup californienne revendique un avantage de 4 foisdu facteur performance/puissance par rapport aux technologies programmables traditionnelles grâce à l’utilisation de blocs configurables pour le routage ou la logique en fonction du circuit mis en œuvre. En septembre de l’année dernière, Efinix a annoncé un tour de financement de 9,5 millions de dollars dirigé par Xilinx, ce qui porte le total des fonds recueillis à environ 16,5 millions de dollars.

Cela fait-il de Xilinx un investisseur majoritaire et donne-t-il à Xilinx un certain pouvoir de contrôle sur la feuille de route d’Efinix? « Tout ce que nous pouvons confirmer, c’est que nous avons investi dans Efinix » était lae réponse plutôt courte donnée…

Parlant de l’investissement Effinix et de diverses autres startups proposant d’intégrer des FPGA dans les ASIC, Peng a déclaré que même si les FPGA embarqués n’étaient pas considérés comme une stratégie d’innovation importante pour Xilinx, l’entreprise pourrait l’activer et si elle devenait stratégique, et alors une acquisition pourrait avoir du sens. Mais pour l’instant, Xilinx a simplement établi un partenariat avec Effinix qui utilise les outils et l’écosystème de codage de Xilinx.

« Le FPGA embarqué ne m’empêche pas de dormir la nuit », a plaisanté le PDG, considérant ce segment de la technologie comme une concurrence négligeable pour une entreprise qui attend la plupart de ses revenus des FPGA haut de gamme.

Pour en revenir à l’architecture ACAP, il vise un large éventail d’applications dans l’ère émergente du big data et de l’intelligence artificielle, et les développeurs de logiciels et de matériel pourront concevoir des produits basés sur ACAP pour des applications finales, edge et cloud. Travaillant sur la mise en œuvre physique, Peng a révélé que la première famille de produits ACAP, baptisée « Everest », serait développée dans la technologie TSM 7nm, avec plus de 50 milliards de transistors et plus d’un milliard de dollars de dépenses R & D.

Avec cette nouvelle ligne de produits, Xilinx vise à faire des centres de données son segment de croissance prioritaire, tout en accélérant la croissance de ses principaux marchés et en prenant la tête de ce qu’elle considère comme une nouvelle ère de l’informatique adaptative.

Les développeurs de logiciels seront en mesure de cibler les systèmes basés sur ACAP en utilisant des outils tels que C / C ++, OpenCL et Python. Un ACAP peut également être programmé au niveau RTL à l’aide d’outils FPGA et Xilinx a déclaré que plus de 1 500 ingénieurs en matériel et logiciel étaient en train de concevoir «ACAP et Everest» dans l’entreprise. Des outils logiciels ont été livrés à des clients clés. En ce qui concerne les comparaisons de performances, « Everest » devrait atteindre une amélioration des performances de 20x sur les réseaux neuronaux profonds par rapport au dernier FPGA Virtex VU9P 16nm d’aujourd’hui et les têtes radio 5G basées sur « Everest » auront 4x la bande passante par rapport aux dernières radios 16nm.

Xilinx – www.xilinx.com

La rédaction vous conseille:

La Startup Efinix réinvente le FPGA

Related articles in English:

CEO change at Xilinx: former COO Victor Peng to replace retiring Moshe Gavrielov

FPGA startup delivers first product

Xilinx’ Zynq ultrascale+ RFSoC chips integrate the RF signal chain

FPGA startup wins funds from Xilinx, Samsung

Xilinx expands ecosystem around Zync MPSoC

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News