Version 6 pour les ASIC à faible coût de Tiny Tapeout

Le projet d’ASIC à faible coût Tiny Tapeout 6 est ouvert aux soumissions. Il ajoute la gestion de l’alimentation pour toutes les conceptions, la prise en charge des signaux mixtes et des broches analogiques.

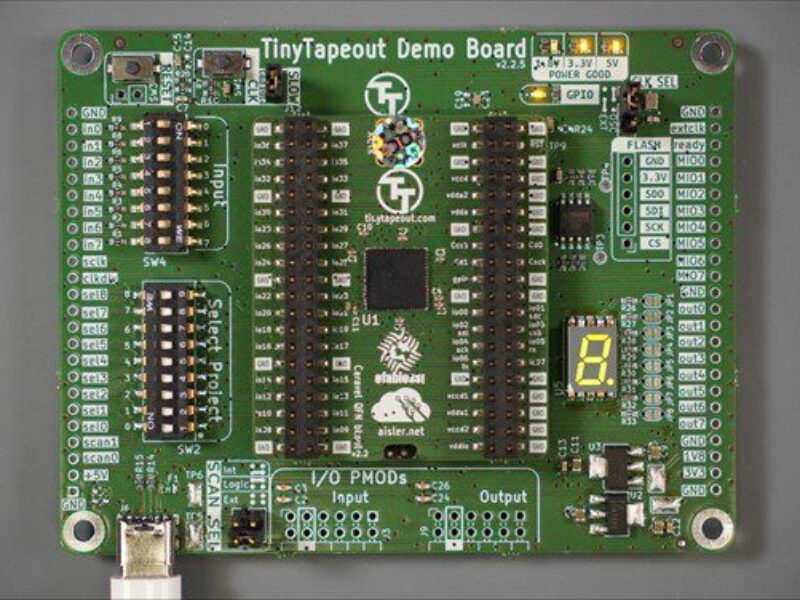

Le Tiny Tapeout 6 a le même espace, les mêmes entrées-sorties et la même vitesse que le précédent Tiny Tapeout 5, mais le power gating ouvre d’autres flux de conception et les soumissions se terminent le 19 avril. Le projet combine des centaines de conceptions ASIC provenant de chercheurs et de développeurs sur une seule puce fabriquée par Skywater selon un procédé de 130 nm, qui est ensuite montée sur une carte.

« Maintenant que toutes les conceptions peuvent être gérées par l’alimentation, nous acceptons les conceptions analogiques, les signaux mixtes et les soumissions réalisées avec d’autres flux ou outils propriétaires. Tant que votre conception respecte les règles DRC du Sky130, vous êtes accepté », a déclaré Matt Venn, l’organisateur du projet. « Si vous souhaitez des broches d’E/S analogiques, le prix est de 40 $ chacune, et votre projet doit utiliser un minimum de 2 tuiles. Le mux analogique est encore en cours de développement et nous prévoyons d’accepter les conceptions nécessitant des broches d’E/S analogiques d’ici le début du mois de mars. »

- Des coûts réduits pour la conception de puces en silicium à source ouverte

- Ouverture des soumissions pour le Tiny Tapeout 5

Les résultats des conceptions sur une série de wafers multiprojets sont attendus pour octobre 2024 et la livraison aux concepteurs pour décembre 2024. Cependant, la pandémie de Covid-19 et les faibles coûts de production ont eu pour conséquence que les projets TT02 n’ont commencé à être expédiés qu’après avoir été testés.

Le prix des wafers multi-projets a également augmenté.

« Lorsque nous avons eu l’idée et la structure de prix de TinyTapeout, le service Efabless chipIgnite proposait 300 puces WLCSP pour 10 000 dollars. Peu de temps après, l’emballage a été remplacé par le type QFN, plus coûteux, et la quantité a été ramenée à 100 », a déclaré M. Venn.

« Avec le triplement du prix des puces, nous avons dû augmenter le prix du matériel pour assurer la viabilité de l’entreprise. La bonne nouvelle, c’est qu’Efabless nous sponsorise toujours, donc les 100 premières soumissions de particuliers n’augmentent que de 50 $, soit 150 $ pour 1 tuile, l’ASIC et la carte de démonstration.

Pour les entreprises, les universités et les particuliers, après les 100 premières ventes, le nouveau prix est de 300 dollars pour une tuile, l’ASIC et la carte de démonstration. Si vous avez besoin de plus d’espace, les tuiles supplémentaires restent au prix de 50 dollars », a-t-il déclaré.

Le récent projet TT05 a fait l’objet de 174 soumissions, utilisant 75 % de l’espace disponible, contre 160 pour TT02. Les conceptions du TT05 comprennent un processeur RISC-V compatible avec Linux, un réseau neuronal programmable, un générateur de sons à table d’ondes et une expérience de métastabilité.

Une nouvelle carte interactive des différents projets est disponible ici.

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News