Un GPU chinois offrant des performances record

La start-up Biren Technology Co. Ltd. (Shanghai, Chine) a lancé sa première puce GPU à usage général, affirmant qu’elle établit un record de performances pour une « monopuce ». Bien que son composant soit en fait un assemblage de puces assez volumineux.

SiPearl et Intel coopèrent sur un GPU pour super-ordinateurs

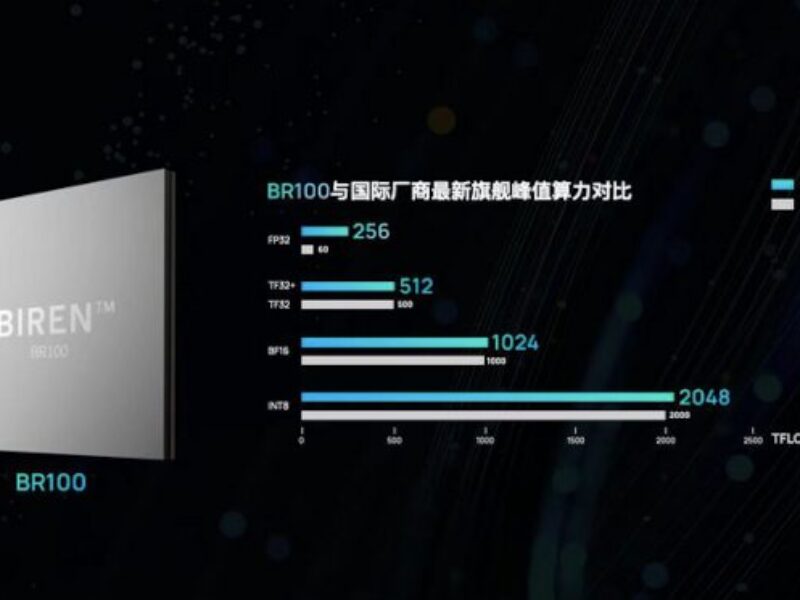

Le BR100 fournit plus de 1 pétaflop de performances en virgule flottante 16 bits et plus de 2 pétaops de performances en virgule fixe 8 bits. La société affirme que c’est trois fois la performance des produits phares vendus par les fabricants internationaux. Biren n’a pas annoncé dans quel processus de fabrication la puce est implémentée ni où elle est fabriquée.

Intel lance un GPU avec 100 milliards de transistors

Biren a été fondée en 2019 et en mars 2021, elle a levé plus de 4,7 milliards de yuans (environ 730 millions de dollars) et revendiqué le statut de « licorne ». Biren a également annoncé sa propre architecture de puce appelée Bi Liren ; Modules serveur Oracle Access Manager (OAM), serveur OAM appelé Haixuan et la plate-forme logicielle Birensupa.

Le BR100 est la première puce GPU à usage général en Chine à adopter la technologie «chiplet», la première à adopter l’interface hôte PCIe 5.0 et la première à prendre en charge le protocole d’interconnexion CXL, déclare la société sur son site Web.

Hong Zhou, CTO de Biren, a déclaré que la raison pour laquelle le BR100 peut surpasser les autres GPGPU est due à son architecture de flux de données Bi Liren sous-jacente et à l’utilisation de chiplets. L’utilisation de chiplets permet une puce beaucoup plus grande que celle autorisée par la taille du masque du circuit intégré. De plus, en réduisant la surface de chaque puce, la capacité de production et le rendement sont améliorés, ce qui réduit le coût des wafers de silicium et prend en charge des stratégies de produits plus flexibles.

Parallèlement au lancement de la BR100, Biren a lancé la BR104. Il s’agit d’un seul chiplet qui fournit environ la moitié des performances du BR100

« La conception Chiplet nous permet d’obtenir deux puces en même temps grâce à un « tapeout » unique, ce qui accélère considérablement la vitesse d’itération et couvre différents niveaux du marché en même temps » a dit Hong Zhou.

Biren est dirigé par le fondateur, président et PDG Zhang Wen.

Related links and articles:

Autres articles sur le sujet:

- Mise à jour de la feuille de route pour le chip européen EPI

- SiPearl vise 1000 collaborateurs en 2025

- Alliances Européennes pour processeurs 2nm et informatique edge

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News