TSMC va présenter des technologies sub-1nm avec transistors 2D

Des chercheurs de la fonderie leader TSMC développent des transistors avec des tailles de caractéristiques inférieures à 1 nm

pour miniaturiser encore plus les conceptions de puces et ont montré le premier transistor à nanofeuilles avec une topologie de porte tout autour (GAA Gate all around)

Un volet de la prochaine conférence sur les dispositifs IEDM en décembre portera sur le développement de transistors 2D utilisant différents matériaux. La conférence, qui célèbre maintenant ses 75 ans, offre une vision importante de la feuille de route pour la miniaturisation continue de la technologie des composants à transistors.

Les chercheurs de TSMC ont travaillé avec des couches de dichalcogénures de métaux de transition (TMD) tels que MoS2 qui ne font qu’un atome d’épaisseur. Un défi majeur de ces matériaux est qu’il est assez difficile de déposer des couches diélectriques sans trous d’épingle, ou des isolants, sur eux. Cela rend difficile leur incorporation dans l’empilement de matériaux qui forme une porte de transistor.

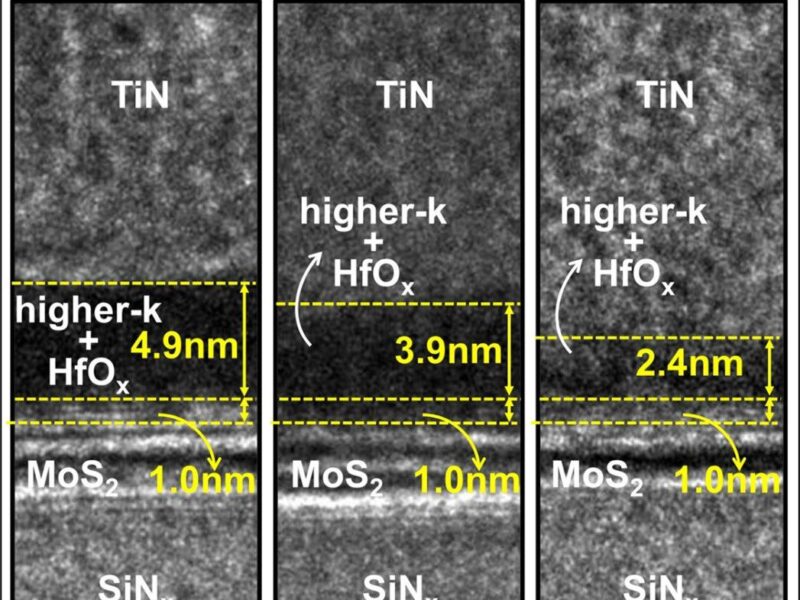

L’équipe a intégré des diélectriques à base d’hafnium formés par dépôt de couche atomique avec le matériau TMD monocouche MoS2, pour construire un nFET à grille sur le dessus avec une épaisseur diélectrique physique de 3,4 nm et une épaisseur d’oxyde électriquement équivalente (EOT) d’environ 1 nm.

L’oscillation sous-seuil (SS) est essentielle dans les transistors MOSFET, et les composants avaient une SS presque idéale de <70 mV/déc.

Une autre équipe de TSMC a également développé le premier transistor à nanofeuilles 2D avec une architecture de grille tout autour (GAA).

Les composants Nanosheet GAA sont considérés comme le candidat le plus prometteur pour les architectures de composants de nouvelle génération car ils offrent un contrôle électrostatique amélioré, un courant de commande relativement élevé et la possibilité de mettre en œuvre des composants de largeurs variables.

Actuellement, la réduction de la longueur de grille et le contrôle électrostatique élevé proviennent de l’amincissement du canal Si, mais à l’avenir, une réduction extrême de la longueur de grille pourrait être permise par l’utilisation de TMD monocouches.

Alors que les nanofeuilles de silicium intégrées à la monocouche TMD comme matériau de canal sont prometteuses, les performances de ces dispositifs et leurs process de fabrication potentiels doivent encore être explorés plus avant.

L’équipe a construit le tout premier FET à nanofeuilles de MoS2 monocouche dans une configuration GAA. Avec une longueur de grille de 40 nm, le transistor présentait une densité de courant d’environ 410 µA/µm à 1 V, obtenue avec un canal monocouche d’environ 0,7 nm d’épaisseur.

Les chercheurs affirment qu’un courant plus élevé peut être obtenu en empilant plusieurs couches de canaux.

Des contacts métalliques à faible résistance de connection aux matériaux 2D sont le goulot d’étranglement pour ces transistors.

Bien que des progrès aient été réalisés avec les contacts de type n à utiliser avec les nFET, les contacts de type p à faible résistance à utiliser avec les pFET sont plus difficiles en raison de l’électro-thermodynamique

Une équipe dirigée par TSMC a mené des études de modélisation et de simulation informatiques pour étudier divers matériaux à utiliser comme contacts de type p avec le matériau 2D WSe2.

Il s’agit notamment de contacts métalliques utilisant un matériau tel que 1T-TiS2 et de contacts semi-métalliques massifs utilisant divers matériaux, dont le Co3Sn2S2 a été identifié comme exceptionnellement bon, avec une résistance de contact théorique aussi faible que 20 Ω·μm.

Paper #7.4, “Nearly Ideal Subthreshold Swing in Monolayer MoS2 Top-Gate nFETs with Scaled EOT of 1 nm,” T-E Lee and Y-C Su et al, TSMC/National Yang Ming Chiao Tung University/National Applied Research Laboratories.

Paper #34.5, “First Demonstration of GAA Monolayer-MoS2 Nanosheet nFET with 410 μA/μm ID at 1V VD at 40nm Gate Length,” Y-Y. Chung et al, TSMC/National Yang Ming Chiao Tung University/National Applied Research Laboratories Taiwan

Paper #28.1, “Computational Screening and Multiscale Simulation of Barrier-Free Contacts for 2D Semiconductor pFETs,” N. Yang et al, TSMC/Penn State Univ./Univ. Florida/Tohoku Univ./Rice Univ./Texas A&M Univ.

Related IEDM articles

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News