Imec présente une cellule CFET à double rangée pour process A7

imec, en Belgique, propose une architecture cellulaire standard pour la logique et la SRAM sur un processus CMOS A7 de 0,7 nm et a développé un prototype sur sa ligne de plaquettes de 300 mm.

Intel, TSMC et Samsung poussent actuellement leurs processus jusqu’à 1,8 nm (18A) et 1,6 nm (16A) avec des transistors à « gates all around » (qu’Intel appelle RibbonFET) et au-delà jusqu’au nœud 14A. Pour les processus ultérieurs, l’imec a mené des recherches sur les transistors empilés à FET complémentaires (CFET) pour les générations suivantes de la feuille de route des processus. La cellule standard est l’étape suivante, combinant le CFET avec le routage.

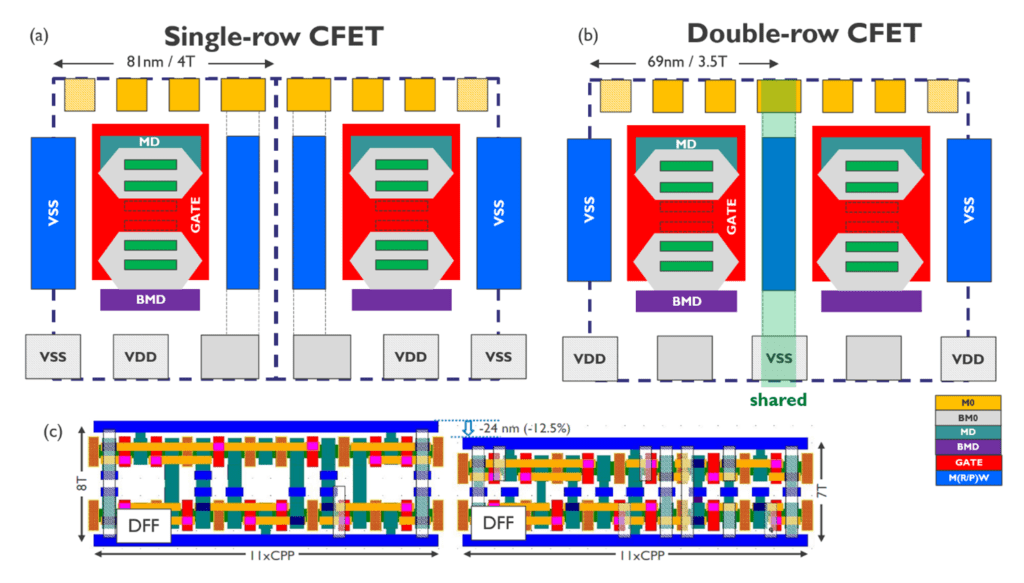

imec présente cette semaine sa cellule standard CFET à l’occasion du 2024 IEEE International Electron Devices Meeting (IEDM). La cellule standard contient deux rangées de CFET avec un mur de routage de signaux partagé entre les deux. Les principaux avantages de cette architecture CFET à double rangée sont la simplification du process et une réduction significative de la surface des cellules logiques et SRAM, selon l’étude DTCO (design-technology co-optimization) de l’IMEC. La nouvelle architecture permet de réduire la hauteur des cellules standard de 4 à 3,5 T, par rapport aux CFET conventionnels à une seule rangée.

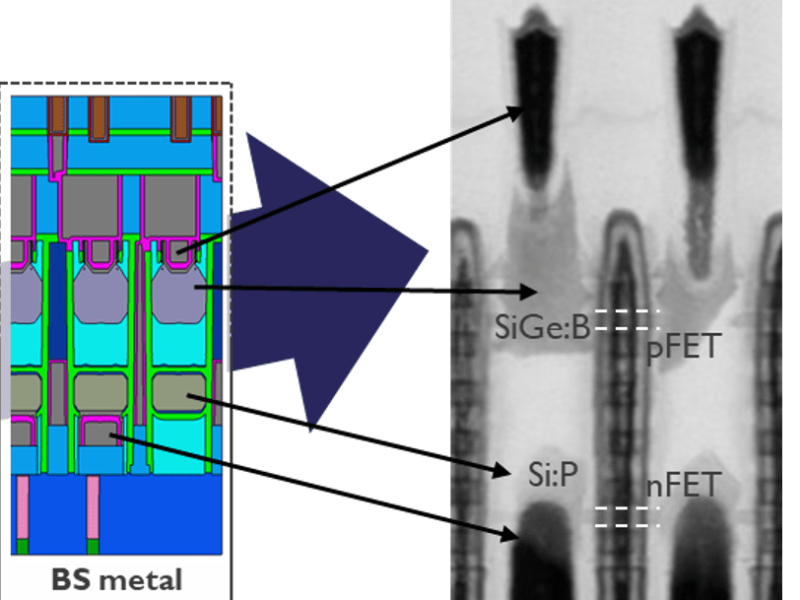

imec présente également à l’IEDM un élément clé de cette architecture CFET à double rangée : un CFET monolithique fonctionnel avec un contact arrière direct avec la source/le drain du dispositif pMOS inférieur, comme il l’avait déjà décrit en juin. Le dispositif a été construit à l’aide d’un modelage EUV de la face arrière qui a assuré un câblage dense de l’alimentation et des signaux de la face arrière et une superposition étroite (<3nm de précision) entre la source/le drain créés à partir de la face avant, le contact de la face arrière et les couches métalliques ultérieures de la face arrière.L’industrie des semi-conducteurs fait des progrès considérables dans la fabrication de dispositifs CFET monolithiques qui sont envisagés pour succéder aux nanofeuillets à grille enveloppante (NSH) dans la feuille de route de la technologie de la logique. L’empilement de dispositifs n- et pFET promet des avantages en termes de puissance, de performance et de surface (PPA) lorsqu’il est associé à des technologies dorsales pour l’acheminement de l’énergie et des signaux.

Au niveau du circuit, cependant, plusieurs options restent ouvertes pour intégrer les CFET dans une cellule standard afin de maintenir ou d’améliorer les avantages escomptés de l’APP. La connectivité au milieu de la ligne (MOL), c’est-à-dire les interconnexions qui relient les contacts de source/drain et de grille aux premières lignes métalliques (à l’arrière et à l’avant) et assurent la connectivité de haut en bas pour l’alimentation et le signal, constitue un défi particulier.

Représentation conceptuelle (a) d’un CFET à une rangée et (b) d’un CFET à deux rangées. La disposition d’une bascule (bascule de type D ou DFF) montre une réduction de la hauteur et de la surface de la cellule de 24 nm (ou 12,5 %) lors de la transition d’un CFET à une rangée à un CFET à deux rangées (H. Kuekner et al., IEDM 2024).

D’après une étude DTCO comparant les architectures de cellules standard, l’imec montre que le CFET à double rangée offre le compromis optimal entre la fabricabilité et l’efficacité de la surface pour les nœuds logiques A7. Cette nouvelle architecture part d’une cellule de base dans laquelle un côté du CFET est optimisé pour les connexions d’alimentation – y compris un rail d’alimentation (VSS) pour fournir de l’énergie de la face arrière au dispositif supérieur et une connexion directe de la face arrière pour le dispositif inférieur. L’autre face est optimisée pour les connexions de signaux en fournissant un mur de routage central (MRW) pour la connectivité de haut en bas. La cellule standard CFET à double rangée (avec deux rangées de dispositifs empilés) est ensuite formée par la mise en miroir de deux cellules de base, qui partagent le même MRW pour la connectivité des signaux.

« Notre étude DTCO montre qu’un MRW partagé pour chaque FET de 3,7 est suffisant pour construire des cellules logiques et SRAM. Cela nous permet de réduire encore la hauteur des cellules standard de 4 à 3,5T, par rapport aux CFET ‘classiques’ à une rangée. Cela se traduit par une réduction significative de la surface de 15 % pour les cellules SRAM », a déclaré Geert Hellings, directeur du programme DTCO chez imec.

« Par rapport aux SRAM construites avec, par exemple, la technologie A14 NSH, les SRAM à double rangée de CFET permettent une réduction de surface de plus de 40 %, ce qui ouvre une nouvelle voie à la mise à l’échelle des SRAM.

Le CFET à double rangée permet également de simplifier le processus en raison de la tranchée MRW partagée entre deux rangées de dispositifs CFET. Il n’est donc plus nécessaire d’utiliser un via supplémentaire à rapport d’aspect élevé pour connecter les dispositifs du haut et du bas, si nécessaire, ce qui réduit la complexité et le coût du traitement MOL.

« Depuis le nœud technologique de 7 nm, l’optimisation des cellules standard par DTCO représente une part de plus en plus importante de l’augmentation de la densité d’un nœud à l’autre, en plus de la mise à l’échelle conventionnelle des dispositifs », a déclaré M. Hellings.

« Pour notre étude DTCO sur les architectures CFET, nous sommes partis des capacités de processus envisagées dans les futures fabs CFET afin de garantir des flux de processus pertinents pour l’industrie. En outre, nous validons notre concept d’usine virtuelle par des preuves de concept technologiques réalisées dans la salle blanche de 300 mm de l’IMEC. Cette combinaison d’activités de fabrication virtuelle et de ligne pilote réelle est une étape cruciale dans l’avancement de nos feuilles de route ».

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News