Le laboratoire de recherche belge imec a démontré les premiers composants CMOS FET complémentaires (CFET) électriquement fonctionnels avec des contacts source/drain inférieurs et supérieurs superposés.

Les composants CFET sont un concurrent clé pour les technologies de traitement de la prochaine génération en dessous de 1 nm. Il s’agit de deux transistors superposés, chacun ayant une longueur de grille de 18 nm, un pas de grille de 60 nm et une séparation verticale de 50 nm entre les dispositifs n et p. La fonctionnalité électrique a été démontrée sur un véhicule d’essai avec des nFET et pFET utilisant une grille commune et des contacts supérieurs et inférieurs connectés par la face avant.

Les composants CFET ont été construits avec les deux contacts modelés sur la face avant, mais l’IMEC a également montré qu’il était possible de déplacer la formation des contacts inférieurs sur la face arrière de la plaquette. Cela améliore considérablement le taux de survie des composants de pointe, qui passe de 11 % à 79 %, et s’appuie sur les travaux clés menés par l’ICEM avec Intel, TSMC et ARM.

La feuille de route de l’imec prévoit l’utilisation de dispositifs CFET dans les architectures de composants au nœud A7 (0,7 nm) et fait suite à la première description des CFET en 2018.

imec looks to process flow for sub-nm stacked CFET transistors

Cependant, la conception des transistors n’est pas la seule question qui se pose pour les technologies de traitement à moins de 1 nm. Les techniques avancées de routage des métaux, y compris l’acheminement de l’énergie et des signaux par l’arrière de la plaquette plutôt que par le haut, peuvent réduire la hauteur des pistes de cellules standard de 20 % sans diminuer les performances.

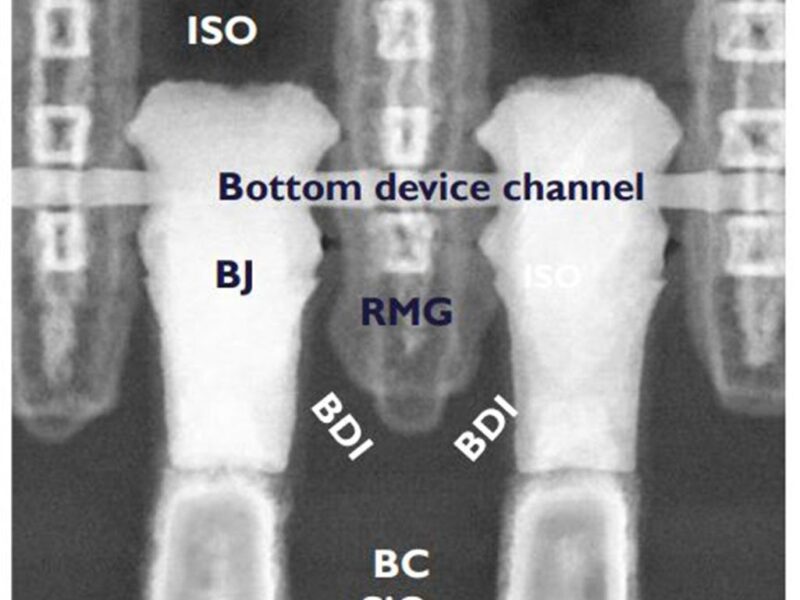

Les composants CFET fonctionnels ont été décrits lors du symposium VLSI 2024, où le flux de processus proposé comprend deux modules spécifiques aux CFET : l’isolation diélectrique médiane (MDI) et les contacts inférieurs et supérieurs empilés.

MDI est un module mis au point par imec pour isoler la grille supérieure et la grille inférieure et différencier les réglages de tension de seuil entre les dispositifs n et p. Le module MDI est basé sur la modification de l’empilement multicouche Si/SiGe « actif » du CFET et permet la co-intégration de l’espaceur interne, une caractéristique spécifique aux feuilles de nanotechnologie qui isole la grille de la source/drain.

« Nous avons obtenu les meilleurs résultats en termes de contrôle des processus grâce à une approche fondée sur le MDI », a déclaré Naoto Horiguchi, directeur de la technologie des dispositifs CMOS à l’IMEC. Avant le retrait source/drain, l’étape où les nanofeuillets et le MDI sont « clivés » pour accéder aux parois du canal et commencer l’épi source/drain. Une gravure innovante de l’évidement source/drain avec ‘in-situ capping’ permet de faire passer le MDI en premier en protégeant le masque dur de la grille/espaceur de la grille pendant l’évidement source/drain ».

Un deuxième module critique est la formation de contacts source/drain inférieurs et supérieurs empilés, séparés verticalement par une isolation diélectrique. Les étapes clés sont le remplissage et la gravure du métal du contact inférieur, puis le remplissage et la gravure du diélectrique – le tout dans le même espace restreint que celui disponible pour la pile MDI.

« En développant les contacts inférieurs à partir de la face avant, nous avons rencontré de nombreux défis, affectant la résistance des contacts inférieurs et limitant la fenêtre de processus pour la formation de la source/drain du dispositif supérieur », a déclaré Horiguchi.

« Au 2024 VLSI, nous montrons qu’il est possible de déplacer la formation du contact inférieur vers la face arrière de la plaquette, malgré les étapes de processus supplémentaires liées au collage et à l’amincissement de la plaquette. Le taux de survie des dispositifs supérieurs est passé de 11 % à 79 %, ce qui fait de la formation de contacts inférieurs sur la face arrière une option intéressante pour l’industrie. Des recherches sont actuellement en cours pour identifier l’approche optimale d’acheminement des contacts ».

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News