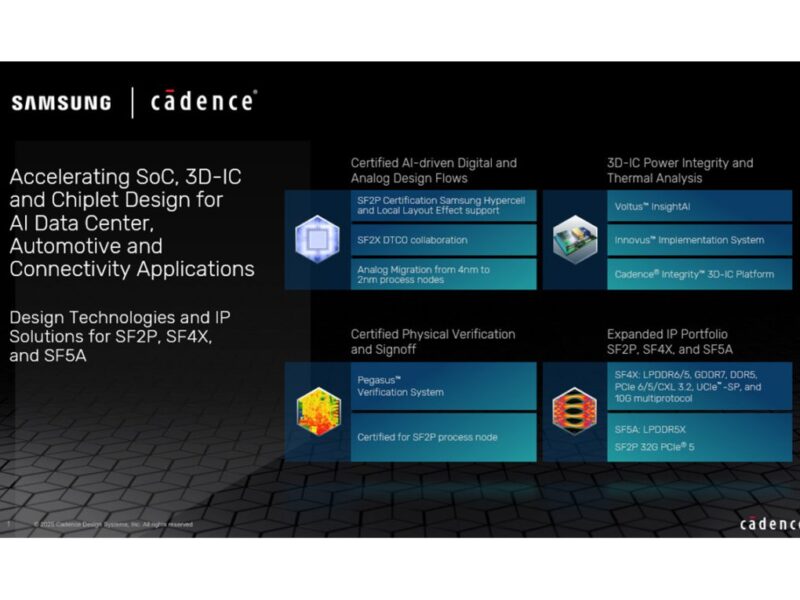

Cadence et Samsung Foundry ont étendu leur collaboration en signant un nouvel accord pluriannuel de propriété intellectuelle et en développant conjointement des flux avancés pilotés par l’IA sur le dernier SF2P et d’autres nœuds de processus avancés. Plus précisément, l’accord pluriannuel sur la propriété intellectuelle permettra d’étendre la propriété intellectuelle de Cadence en matière de mémoire et d’interface dans les nœuds de processus avancés SF4X, SF5A et SF2P de Samsung Foundry.

En s’appuyant sur la technologie de conception pilotée par l’IA de Cadence et sur les nœuds de processus SF4X, SF4U et SF2P avancés de Samsung, cette collaboration vise à fournir des solutions haute performance et basse consommation pour les centres de données d’IA, l’automobile, les ADAS et les applications de connectivité RF de nouvelle génération.

« Nous prenons en charge un portefeuille complet de PI, de sous-systèmes et de chiplets sur les nœuds de process Foundry de Samsung, et notre dernier accord pluriannuel sur la PI renforce notre collaboration continue », a déclaré Boyd Phelps, vice-président senior et directeur général du Silicon Solutions Group chez Cadence. « En combinant la conception et le silicium pilotés par l’IA de Cadence avec les process avancés de Samsung, nous fournissons les technologies de pointe dont nos clients mutuels ont besoin pour innover et mettre leurs produits sur le marché plus rapidement. »

Hyung-Ock Kim, vice-président et responsable de la Foundry Design Technology Team chez Samsung Electronics, a ajouté : « La suite d’outils numériques de Cadence, du RTL au GDS, est désormais certifiée pour le dernier nœud de process SF2P de Samsung, supportant des avancées telles que les technologies Hyper Cell et LLE 2.0. Cadence et Samsung collaborent également étroitement pour permettre la migration analogique, améliorer l’intégrité de l’alimentation et les analyses thermiques et de déformation pour les circuits intégrés 3D utilisant l’accélération GPU. De plus, un accord pluriannuel entre Cadence et Samsung Foundry pour étendre les solutions de mémoire et d’interface IP renforce encore notre partenariat ».

Le nouvel accord pluriannuel fournira des mémoires et des interfaces IP avancées conçues pour l’IA, le calcul à haute performance (HPC) et les applications automobiles. Le portefeuille élargi d’IP SF4X comprend LPDDR6/5x-14.4G, GDDR7-36G, DDR5-9600, PCI Express (PCIe) 6.0/5.0/CXL 3.2, Universal Chiplet Interconnect Express (UCIe)-SP 32G, et 10G multi-protocoles PHY (USB3.x, DP-TX, PCIe 3.0, et SGMII) avec l’IP de contrôleur compagnon, permettant un silicium de sous-système complet. L’IP PHY LPDDR5X-8533, conçu pour les applications automobiles, complète la plateforme IP SF5A, tandis que l’introduction d’un nouveau PHY PCIe 5.0 32G dans l’offre SF2P existante répond aux exigences des principaux clients AI/HPC.

Basé sur un vaste projet de conception et de co-optimisation technologique (DTCO), le flux numérique complet de Cadence a été certifié pour le dernier nœud de process SF2P de Samsung, y compris la méthodologie Hyper Cell de Samsung. De plus, Cadence a mis en place un support pour la précision temporelle de Samsung Local Layout Effect (LLE). Cadence et Samsung collaborent également sur le DTCO pour les nœuds de processus de la prochaine génération.

Le système de vérification Cadence Pegasus est certifié pour Samsung SF2P et d’autres nœuds Samsung. Le flux de vérification physique de Cadence est optimisé pour permettre aux clients mutuels d’atteindre les objectifs de précision de signature et de temps d’exécution avec une évolutivité massive, permettant ainsi un temps de mise sur le marché plus rapide.

Pour faire face à la migration des conceptions analogiques, Cadence et Samsung Foundry ont automatisé avec succès le transfert de la propriété intellectuelle basée sur des cellules analogiques de 4 nm vers le nœud de process avancé de 2 nm, ce qui permet des délais d’exécution plus rapides tout en conservant l’intention fonctionnelle et de conception. Cette migration souligne l’importance de la mise à l’échelle de la technologie et de la réutilisation de la propriété intellectuelle pour minimiser les délais et les coûts de développement, ouvrant ainsi la voie à de futures migrations de cellules analogiques et d’autres éléments de propriété intellectuelle entre différents nœuds de process.

Les deux entreprises ont également démontré avec succès un flux complet de co-conception de modules frontaux (FEM) et d’antennes en boîtier (AiP) pour les applications mmWave de la prochaine génération basées sur le process FinFET 14 nm de Samsung. Le délai de conception a été accéléré grâce à la rationalisation de la gestion des données de conception à chaque étape du développement d’un circuit intégré ou d’un module, depuis la budgétisation initiale au niveau du système jusqu’à la co-conception, l’analyse et la vérification post-mise en page des circuits intégrés et des boîtiers RFIC.

Cadence et Samsung ont également collaboré à une analyse complète de l’intégrité de l’alimentation pour les circuits intégrés 3D, couvrant l’ensemble du processus, de l’exploration initiale à la validation finale, en utilisant les outils EDA avancés de Cadence, notamment Voltus InsightAI, Innovus Implementation System et Integrity 3D-IC Platform. Appliqué à une puce CPU à haute vitesse utilisant le nœud SF2 de Samsung, Voltus InsightAI a atteint une résolution impressionnante de 80-90% des violations IR-drop avec un impact minimal sur la synchronisation et la puissance, démontrant sa capacité à équilibrer l’intégrité de la puissance avec les besoins de performance.

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News