SiFive a lancé un processeur RISC-V IP avec un moteur matriciel et une extension personnalisée pour la première fois pour les applications d’intelligence artificielle.

Les IP XM Series de SiFive comprennent un moteur matriciel d’IA hautement évolutif pour les puces Edge AI et IoT ainsi que pour les appareils grand public, les véhicules électriques et/ou autonomes de nouvelle génération et les centres de données.

SiFive a également annoncé son intention d’ouvrir à la source une implémentation de référence de sa SiFive Kernel Library (SKL).

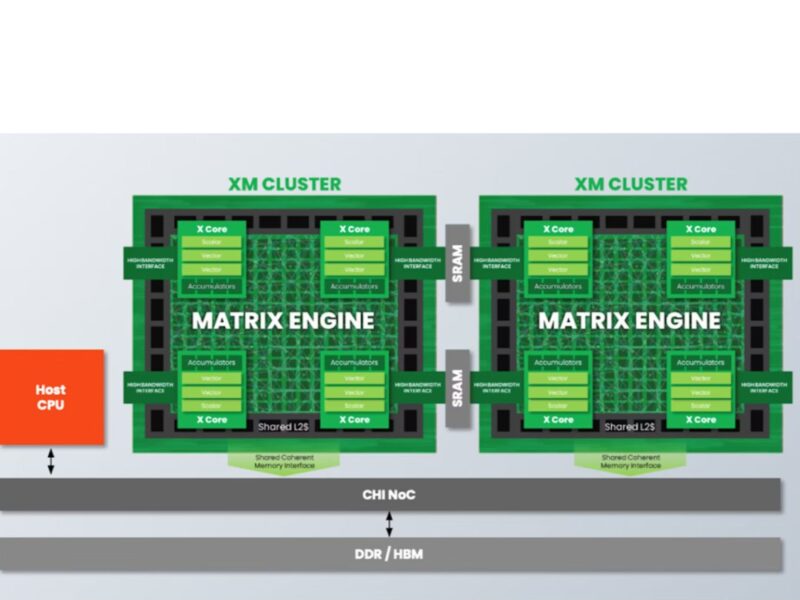

Le XM intègre des moteurs scalaires, vectoriels et matriciels pour résoudre les problèmes de bande passante de la mémoire des conceptions d’IA. Il y a quatre X-Cores par cluster, chacun avec deux unités vectorielles, et un cluster peut fournir 16 TOPS (INT8) ou 8 TFLOPS (BF16) par GHz. X-Cores par cluster. Il peut exécuter toutes les autres couches, par exemple les fonctions d’activation, et ajoute de nouvelles instructions d’accélération exponentielle personnalisées.

Les nouvelles instructions matricielles sont récupérées par l’unité scalaire, les données sources provenant des registres vectoriels, et les résultats sont envoyés à chaque accumulateur matriciel.

Chaque grappe de la série XM dispose d’une bande passante mémoire soutenue de 1 To/s. Les grappes peuvent accéder à la mémoire via un port à large bande vers la SRAM pour les données de modèle ou via un port CHI pour l’accès cohérent à la mémoire.

« De nombreuses entreprises constatent les avantages d’un standard de processeur ouvert alors qu’elles s’efforcent de suivre le rythme rapide de l’évolution de l’IA. L’IA joue sur les forces de SiFive avec la performance par watt et notre capacité unique à aider les clients à personnaliser leurs solutions « , a déclaré Patrick Little, PDG de SiFive.

« RISC-V a été développé à l’origine pour prendre en charge efficacement les moteurs de calcul spécialisés, y compris les opérations en précision mixte », a déclaré Krste Asanovic, fondateur et architecte en chef de SiFive. « Cette caractéristique, associée à l’inclusion d’instructions vectorielles efficaces et à la prise en charge d’extensions spécialisées dans l’IA, est la raison pour laquelle bon nombre des plus grandes entreprises de centres de données ont déjà adopté les accélérateurs d’IA RISC-V. »

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News