Les trois grands de l’EDA soutiennent les chiplets ARM pour l’automobile

Cadence, Siemens et Synopsys visent à stimuler l’utilisation des cœurs automobiles d’ARM dans les chiplets et les systèmes sur puce grâce à une série d’outils. Cependant, Synopsys est pour l’instant absente de la série d’annonces orchestrées.

Synopsys est également l’un des principaux soutiens d’ARM dans le secteur automobile et l’un des principaux développeurs d’outils de conception de chiplets et d’IP. Toutefois, elle dispose de ses propres cœurs IP concurrents basés sur l’architecture ARC et RISC-V, et poursuit actuellement l’acquisition du fabricant d’outils de simulation Ansys pour un montant de 35 milliards de dollars.

Avec ARM, la conception de référence du chiplet ADAS et la plateforme de développement logiciel développées par Cadence visent à accélérer la mise sur le marché des véhicules définis par logiciel (SDV) pour ses propres accélérateurs d’IA.

« L’évolution de l’industrie automobile vers le véhicule défini par logiciel signifie que les processus traditionnels de développement de logiciels et de matériel ne sont plus valables et doivent évoluer pour répondre aux exigences de l’industrie. Notre partenariat avec ARM, qui prend en charge l’environnement de simulation accélérée avec le processeur Cortex-A720 AE, contribue à relever les défis de l’industrie automobile en réduisant le délai de mise sur le marché des logiciels SDV grâce à la disponibilité de plates-formes automobiles accélérées bien avant le silicium », a déclaré Mike Ellow, vice-président exécutif, Electronic Design Automation, Siemens Digital Industries Software.

- Premiers modèles de simulation thermique sécurisés pour les amplificateurs de puissance à chiplets

- Cadence se lance dans l’analyse structurelle avec une opération de 1,2 milliard de dollars

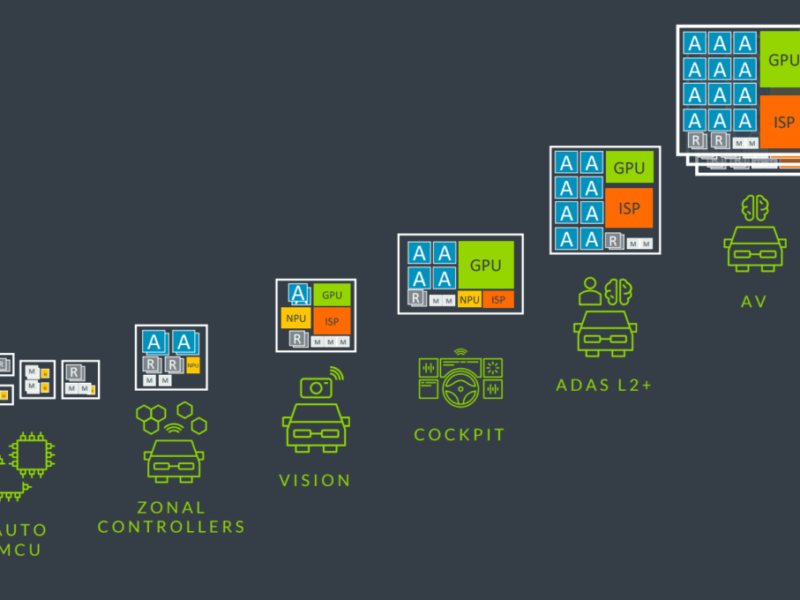

La conception de référence automobile de Cadence, initialement destinée aux systèmes avancés d’aide à la conduite (ADAS), spécifie une architecture de chiplets évolutive et une interopérabilité d’interface avec le protocole UCIe et l’IP.

La plate-forme de développement de la pile logicielle est fournie sous la forme d’un jumeau numérique du matériel conforme à la norme logicielle de l’initiative SOAFEE (Scalable Open Architecture for Embedded Edge). Cela permet de commencer le développement du logiciel avant que le matériel ne soit disponible et de valider ensuite l’intégration du système.

- Synopsys s’attaque à ARM au sujet des processeurs de sécurité ASIL-D

- Synopsys rachète Ansys pour 35 milliards de dollars dans le domaine de la simulation

Cadence considère que les chiplets et les 3D-Ics constituent une architecture de plus en plus populaire pour les conceptions automobiles, mais ils ont également besoin d’un support logiciel en amont.

L’architecture et la conception de référence fournissent une norme pour l’interopérabilité de l’interface chiplet avec Helium Virtual and Hybrid Studio pour la création rapide de plateformes virtuelles et hybrides et Helium Software Digital Twin pour soutenir le déploiement à l’échelle pour les développeurs de logiciels.

La propriété intellectuelle comprend l’unité de traitement neuronal Neo (NPU), le kit de développement logiciel (SDK) NeuroWeave pour les solutions d’apprentissage automatique (ML) et le DSP de Tensilica.

« L’industrie automobile évolue rapidement et les avancées en matière d’IA et de logiciels soulignent un besoin accru d’accélérer les cycles de développement », a déclaré Dipti Vachani, vice-président senior et directeur général de la ligne d’activité automobile d’ARM. « En collaboration avec des partenaires critiques de l’écosystème comme Cadence, nous accélérons le développement de logiciels et de matériel en rassemblant une solution complète de technologies de conception et de vérification étayées par les dernières technologies Automotive Enhanced d’Arm, ce qui permet aux développeurs de commencer à construire pour les SDV de la prochaine génération bien avant que le silicium ne soit disponible sur le marché. »

« La réduction de la charge de travail globale liée à la conception du système et le déplacement du développement du matériel et du logiciel sont tous deux essentiels pour respecter les délais de mise sur le marché de plus en plus courts lors du développement des SDV de plus en plus complexes d’aujourd’hui. Les plates-formes virtuelles et les chiplets sont deux outils clés pour les développeurs de SoC 3D-IC pour l’automobile », a déclaré Paul Cunningham, vice-président senior et directeur général du groupe de vérification des systèmes chez Cadence.

« La quantité croissante d’électronique dans les voitures et la transition vers des véhicules définis par logiciel exigent de tirer parti de jumeaux numériques de l’électronique pour remodeler le cycle de développement automobile et accélérer l’innovation. La collaboration de longue date de Synopsys avec ARM et son écosystème fournit aux développeurs automobiles des solutions de pointe, depuis l’exploration précoce de l’architecture jusqu’au test rapide des logiciels automobiles et à la validation des systèmes pour les conceptions basées sur les dernières IP de processeurs ARM améliorées pour l’automobile « , a déclaré Tom De Schutter, vice-président de l’ingénierie, Systems Design Group, chez Synopsys.

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News