Le processeur SoW Dojo de Tesla en production chez TSMC

Le processeur Dojo de 25 puces du constructeur automobile Tesla est en cours de production chez TSMC, selon des informations recueillies lors du symposium technologique nord-américain du fondeur qui s’est tenu récemment à Santa Clara, en Californie.

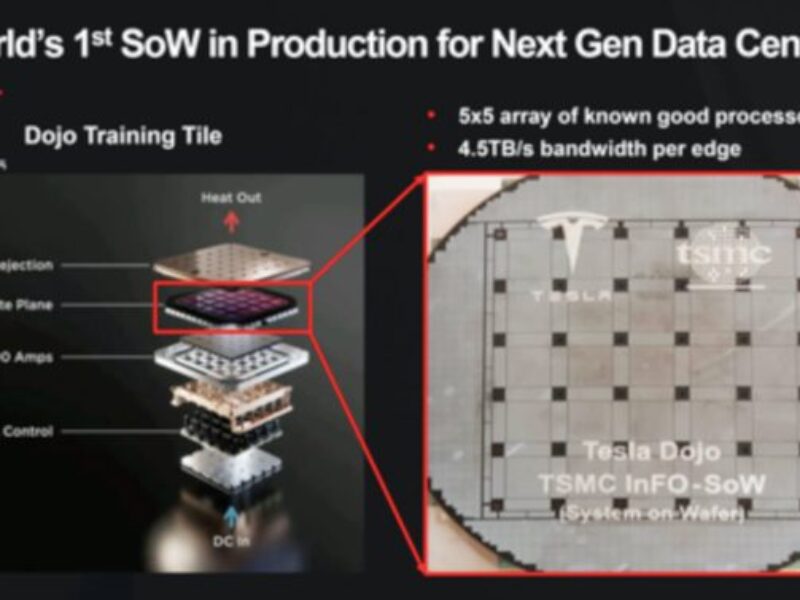

TSMC l’a décrit comme « le premier système sur wafer au monde en production pour les centres de données de la prochaine génération ».

Le processeur Dojo, est un réseau de 5 processeurs D1 AI placés sur un wafer de support et interconnectés à l’aide de la technologie InFO (Integrated Fan-Out) de TSMC pour créer un système sur wafer (SoW).

Dojo est un superordinateur conçu par Tesla pour exécuter des modèles d’apprentissage automatique afin de soutenir le système avancé d’aide à la conduite Full Self-Driving (FSD). Le Tesla D1 est un processeur d’inférence et d’apprentissage de l’IA développé en interne et composé d’environ 50 milliards de transistors fabriqués à l’aide du process de fabrication 7nm de TSMC. Chaque D1 offre une capacité de calcul de 362 Tflops. De nombreuses tuiles de ce type sont incorporées dans un superordinateur, bien que la consommation de courant et la production de chaleur soient apparemment problématiques.

Packaging à l’échelle du wafer de TSMC

La première installation de supercalculateurs Dojo a commencé à Palo Alto, en Californie, et Tesla a construit un centre de données Dojo à son siège d’Austin, au Texas. Tesla a également annoncé un projet de 500 millions de dollars pour la construction d’une grappe de superordinateurs à Buffalo, dans l’État de New York.

TSMC aurait déclaré lors du symposium qu’elle prévoyait de proposer un conditionnement plus complexe à l’échelle du wafer en 2027. Cela permettrait d’obtenir jusqu’à 40 puces de la taille d’un réticule et jusqu’à 60 puces de mémoire à large bande sur une tranche de silicium.

TSMC est le fournisseur de fonderie de Cerebras Systems Inc. qui fabrique déjà des processeurs multi-puces rectangulaires à l’échelle de la plaquette. Cerebras a récemment lancé son accélérateur d’IA de troisième génération à l’échelle du wafer. L’accélérateur CS-3 compte plus de 4 milliards de transistors dans 900 000 cœurs. Il est deux fois plus rapide que son prédécesseur et établit des records en matière d’apprentissage de grands modèles linguistiques et multimodaux. L’entreprise a utilisé son accélérateur CS-2 pour fournir un superordinateur d’IA de 4exaFLOP en 2023.

Liens et articles connexes :

Articles de presse :

TSMC prévoit un processus de 1,6 nm pour 2026

Tesla signe un accord de fourniture de puces indiennes avec Tata, selon un rapport

Cerebras présente un processeur d’IA de troisième génération à l’échelle de la plaquette

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News