Intel et TSMC détailleront leur process 2nm à l’IEDM

Les tentatives d’Intel pour revenir à la pointe de la fabrication de puces et les mesures prises par le fondeur TSMC pour définir cette pointe seront exposées lors de la réunion internationale des dispositifs électroniques (IEDM) qui se tiendra cette année en décembre à San Francisco.

Dans un document d’actualité, des chercheurs de TSMC dévoileront le process de fabrication N2, qui est un process nominal de 2 nm conçu pour l’informatique dans les domaines de l’IA, de l’informatique mobile et de l’informatique à haute performance. Dans l’article suivant de la même session, les ingénieurs d’Intel fourniront des détails sur la mise à l’échelle des RibbonFET, le nom qu’Intel donne à ses transistors à nanofeuillets.

Lors de la conférence IEDM, les chercheurs de TSMC devraient annoncer que le procédé N2 offre un gain de vitesse de 15 % ou une réduction de puissance de 30 %, avec une densité de puce améliorée de 15 % ou plus par rapport à son propre procédé N3 (3 nm nominal) introduit en 2022.

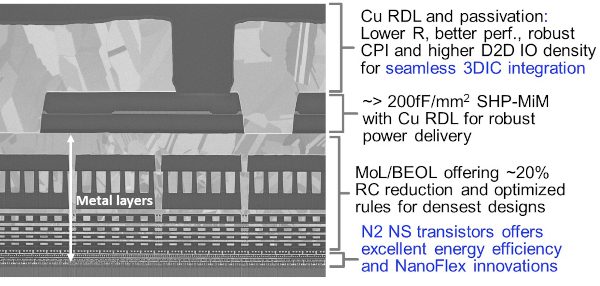

Coupe transversale d’une pile d’interconnexion N2 montrant la couche de redistribution du cuivre. Source : IEDM et T l’image en coupe montre que la couche de redistribution du cuivre (RDL) et la passivation de la plate-forme N2 permettent une intégration transparente avec les technologies 3D.

Le document 2.1 2nm Platform Technology Featuring Energy-Efficient Nanosheet Transistors and Interconnects Co-Optimized with 3DIC for AI, HPC and Mobile SoC Applications, rédigé par G. Yeap et all de TSMC, devrait également présenter une macro SRAM avec une densité record de 38 Mbits par millimètre carré.

L’article présentera également des détails sur l’interconnexion au milieu (MEOL) et en fin de ligne (BEOL) qui comprend une couche de redistribution évolutive à base de cuivre pour un placement flexible des plots d’entrée/sortie avec une résistance de barrière réduite, une couche de passivation plate (pour une fiabilité accrue) et des vias à travers le silicium, ou TSV (pour l’interconnexion des composants dans différentes couches).

Les chercheurs affirment que la plateforme N2 a satisfait aux exigences de fiabilité au niveau des plaquettes et aux tests de qualification initiaux. La qualification complète est prévue pour 2025 et la production de masse pour 2026.

Intel

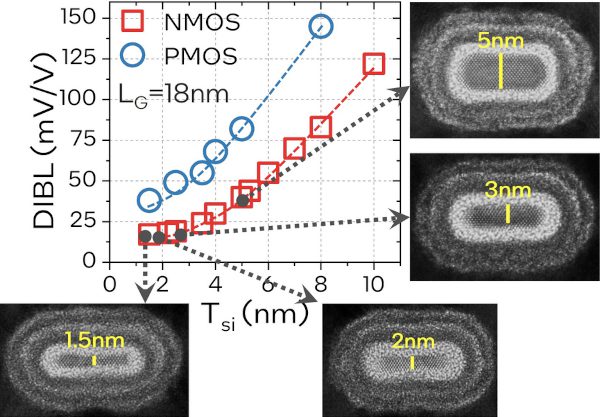

Dans le document 2.2 Silicon RibbonFET CMOS at 6nm Gate Length, A. Agrawal et all d’Intel montrent comment ils ont construit la technologie des nanofeuillets (RibbonFET) avec des portes de 6nm et un pas de polysilicium contacté de 45nm (CPP, l’espacement entre les portes des transistors) sans dégradation de la mobilité des électrons.

Abaissement de la barrière induit par le drain (DIBL) en fonction de l’épaisseur de silicium (Tsi) à une longueur de grille de 18 nm. On observe une réduction lorsque Tsi passe de 10 nm à 1,5 nm ; toutefois, la réduction de DIBL est saturée à Tsi <4 nm. La DIBL du PMOS est plus élevée que celle du NMOS à la même Tsi. Vous trouverez également des micrographies TEM d’un transistor 1NR avec différentes valeurs de Tsi jusqu’à 1,5nm. Source : IEDM : IEDM.

Les auteurs ne font pas référence à un processus de fabrication spécifique d’Intel, mais il est prévu que les RibbonFET soient introduits dans la production dans le process 20A – process nominal de 20 angstroms ou 2nm. Intel a apparemment choisi de n’introduire aucun de ses produits processeurs en 20A et de passer directement de son process 3nm au processus 18A, ce qui peut se refléter dans l’accent mis par les auteurs sur la mise à l’échelle des nanofeuillets.

Les chercheurs montreront que la mobilité des électrons ne se dégrade pas jusqu’à une épaisseur de silicium de 3 nm. Ensuite, la diffusion des électrons due à la rugosité de la surface devient un problème. Dans l’article, les auteurs expliquent comment le contrôle des canaux courts en dessous d’une épaisseur de silicium de 4nm et l’ingénierie des fonctions de travail permettent d’obtenir des tensions de seuil basses avec 3nm comme valeur de référence.

Liens et articles connexes :

Articles de presse :

Intel et TSMC s’apprêtent tous deux à présenter des CFET empilés à l’IEDM

Aucune date n’a été fixée pour la fourniture par Samsung des puces 2nm de Preferred Networks

Rapidus inaugure la construction d’une usine de fabrication de 2 nm et embauche à tour de bras

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News