Intel et le CEA-Leti développent des matériaux 2D pour les futurs transistors

Le géant des puces électroniques Intel et l’institut de recherche français CEA-Leti, basé à Grenoble, ont déclaré qu’ils allaient collaborer pour développer des technologies de transistors basées sur des dichalcogénures bidimensionnels de métaux de transition (TMD).

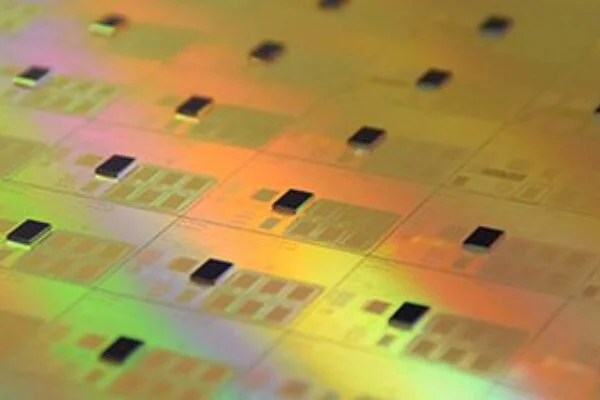

Ces matériaux – tels que les TMD à base de molybdène et de tungstène – sont décrits comme des options prometteuses pour les matériaux de canal pour les transistors à échelle réduite. Le CEA-Leti et Intel ont créé un projet de recherche commun pluriannuel pour développer la technologie de transfert de couches de dichalcogénures bidimensionnels de métaux de transition (2D TMD) sur des wafers de 300 mm. Ces technologies pourraient être utiles pour les process de fabrication sub-nanométriques déployés au-delà de 2030, a déclaré le CEA-Leti.

Les semiconducteurs en couches 2D offrent une épaisseur innée de canal de transistor inférieure au nanomètre, ce qui les rend appropriés pour les plates-formes à haute performance et à faible consommation d’énergie en raison de leur bon transport de porteurs et de leur mobilité, même pour les couches atomiquement fines. En outre, l’épaisseur du corps du composant et la bande interdite énergétique modérée permettent d’améliorer le contrôle électrostatique et, par conséquent, de réduire les courants à l’état bloqué.

Ces caractéristiques font des dispositifs à transistors 2D-FET empilés une solution prometteuse pour la mise à l’échelle des transistors au-delà de 2030, a déclaré le CEA-Leti. Toutefois, cela nécessitera des méthodes pour la croissance des canaux 2D et le transfert vers la technologie des wafers de silicium.

L’objectif du projet est de créer un process viable pour la croissance de matériaux 2D de haute qualité sur des substrats de 300 mm et leur transfert vers un autre substrat de composants pour l’intégration du processus du transistor.

Repousser la loi de Moore

« Alors que nous repoussons sans cesse la loi de Moore, le matériau 2D TMD est une option prometteuse pour repousser les limites de la mise à l’échelle des transistors à l’avenir », a déclaré Robert Chau, senior fellow d’Intel pour le développement technologique, dans un communiqué publié par le CEA-Leti.

M. Chau a quitté les États-Unis pour s’installer en Europe en 2022 afin de diriger la recherche européenne d’Intel et de piloter la R&D d’Intel avec ses partenaires sur le continent.

Sébastien Dauvé, PDG du CEA-Leti, a déclaré qu’en raison de la température de croissance élevée des matériaux, qui dépasse 700 degrés C, il est difficile de déposer des empilements sous forme de couches minces et que le transfert de couches est le plus prometteur pour les intégrer dans de futurs composants.

Liens et articles connexes :

Articles de presse :

Un alliage de germanium et d’étain pour les futurs transistors

Des transistors « en croissance » sur les puces électroniques

L’IMEC présente un CFET monolithique lors d’un symposium VLSI

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News