Intel ajoute l’IA à l’outil FPGA Quatrus d’Altera

Intel ajoute la prise en charge de l’IA à ses outils FPGA Quartus, à l’occasion de la scission de cette activité sous le nom d’Altera.

« Alors que les clients sont confrontés à des défis technologiques de plus en plus complexes et s’efforcent de se différencier de leurs concurrents et d’accélérer le temps de retour sur investissement, nous avons l’opportunité de revigorer le marché des FPGA », a déclaré Sandra Rivera, PDG d’Altera, qu’Intel envisage de céder au cours des deux prochaines années.

- Intel finalise l’acquisition d’Altera

- La nouvelle version du logiciel de conception d’Altera prend en charge les DSP

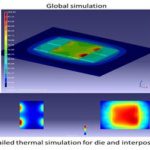

Quartus a été développé par Altera pour répondre à la complexité de la conception des FPGA et a ajouté la capacité DSP en 2014 avant l’acquisition par Intel. Intel ajoute des capacités d’IA faciles à intégrer afin de tirer parti de la croissance rapide du marché de l’IA, en particulier pour l’Agilex 5, dont les blocs DSP ont été améliorés pour prendre en charge les calculs Tensor de l’IA.

La mise à jour de Quartus inclut la FPGA AI Suite et OpenVINO, qui génèrent une propriété intellectuelle (IP) optimisée basée sur des frameworks standards tels que TensorFlow et Pytorch.

Intel plans to IPO its FPGA business

Les FPGA Agilex 5 sont construits dans un process de 7nm et sont maintenant en production de masse. Il s’agit également du premier système de processeur d’application « asymétrique » doté d’un processeur ARM Cortex-A76 à double cœur et d’un processeur ARM Cortex-A55 à double cœur sur une puce monolithique. Contrairement aux FPGA AMD/Xilinx qui utilisent des chiplets d’accélération de l’IA distincts.

L’Agilex 5 comprend des émetteurs-récepteurs GTS à grande vitesse jusqu’à 28,1 Gbit/s et un support PCI Express 4.0 ×8, ainsi qu’une interface de mémoire externe DDR5 jusqu’à 4 000 Mbit/s.

Les FPGA Agilex 9 sont également maintenant produits en volume avec des convertisseurs de données à grande vitesse pour des applications radar et militaires-aérospatiales qui nécessitent des FPGA à signaux mixtes à large bande passante.

Les composants Agilex 7 F-series et I-series sont mis en production afin d’améliorer la performance par watt des centres de données, des réseaux et des applications de défense. Ils utilisent le chiplet R-Tile pour ajouter des capacités PCIe 5.0 et CXL et c’est le seul FPGA avec une propriété intellectuelle (IP) supportant ces interfaces.

Agilex 3 est conçu comme une gamme de FPGA à faible consommation d’énergie et à valeur ajoutée pour des fonctions peu complexes destinées aux applications de cloud, de communication et edge intelligente.

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News