Infineon réduit de moitié l’épaisseur des wafers de puissance

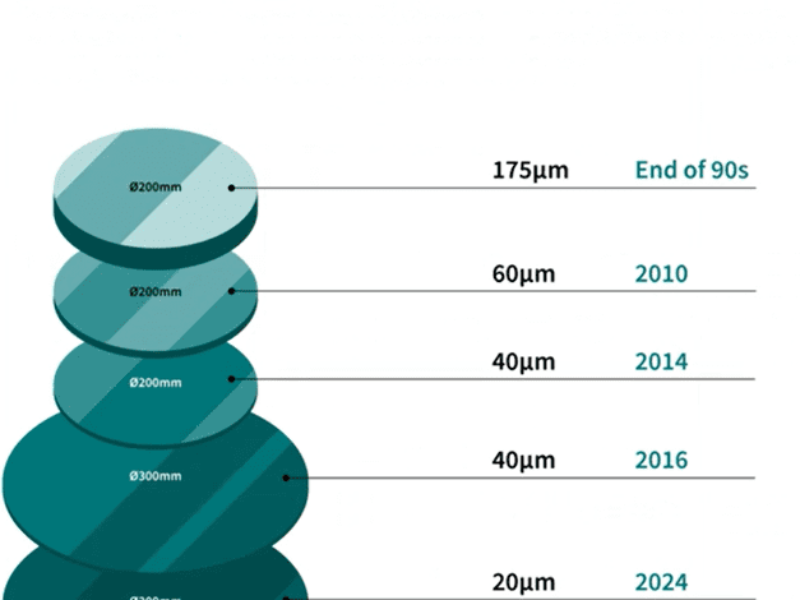

Infineon a réduit de moitié l’épaisseur de ses wafers de puissance en silicium, la ramenant à 20 µm, ce qui a permis de réduire la résistance à l’enclenchement RDS-on de 40 % et les pertes de puissance globales de 15 %.

« Il s’agit d’une avancée technologique importante de la part d’Infineon, le wafer de puissance le plus fin avec une épaisseur stupéfiante de 20 microns », a déclaré Adam White, résident de la division des systèmes de puissance et de capteurs d’Infineon. « Cela permet de réduire la résistance du substrat de la plaquette de 50 % et les pertes de puissance de 15 %. En réduisant l’épaisseur de la plaquette, vous obtenez des pertes de puissance réduites dans le système.

Le processus, développé à Villach en Autriche, sera utilisé pour les composantys 12V pour la conversion d’énergie locale pour la prochaine génération de GPU, TPU et CPU d’IA. Ces composants nécessitent des courants élevés de 1 000 à 2 000 A à des tensions de 0,8 V à partir d’un rail d’alimentation de 5 V, 12 V ou 48 V, et il existe de multiples topologies pour y parvenir, explique M. White.

« Pour les transistors de 10 à 12 V, cela permet de réduire le RDSon de 40 %, ce qui est inégalé, et nous pensons donc que l’industrie s’intéressera beaucoup aux transistors de 40 V et moins. Nous avons déjà pris contact avec des clients dans le domaine de l’intelligence artificielle. Parmi les autres applications, citons les produits grand public, la commande de moteurs et l’informatique.

« Il y a également un gain d’efficacité de 3 % à 50 A grâce à l’optimisation de la conception des puces, à de nouvelles conceptions de circuits d’attaque et aux MOSFET de la prochaine génération qui seront construits sur cette technologie ultramince », a-t-il déclaré. Les plaquettes plus fines permettent également de réaliser des connexions d’alimentation à l’arrière avec moins d’efforts.

M. White est réticent à parler de la manipulation requise pour les plaquettes plus fines. « Les systèmes et la manipulation des plaquettes de 300 mm sont les principaux obstacles à surmonter », a-t-il déclaré. « Il s’agit vraiment d’une manipulation spécialisée, mais nous devons suivre des étapes spéciales.

Le processus est similaire à celui des plaquettes de 40um lancées en 2016, mais il comporte des étapes supplémentaires. « Cela montre le temps qu’il a fallu pour le mettre au point », a déclaré M. White. « Il n’y a pas de coût supplémentaire, nous n’introduisons pas un processus qui nécessite des investissements supplémentaires, nous ajoutons quelques étapes pour descendre à 20 microns. Lorsque vous traitez des plaquettes sur des substrats en silicium, le traitement est tout à fait remarquable », a-t-il déclaré à eeNews Europe et ECInews.

Le procédé de fabrication des plaquettes de silicium sera utilisé avec le carbure de silicium et le nitrure de gallium.

« Nous devons maîtriser les trois technologies et le silicium continuera à dominer dans un certain nombre de domaines », a-t-il déclaré. « Notre montée en puissance à Kulim sur les plaquettes SiC de 200 mm se déroule comme prévu, et nous avons également annoncé la première plaquette de puissance GaN de 300 mm au monde, qui présente des avantages à haute fréquence, c’est-à-dire au-delà de 5 MHz.

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News