Synopsys mise sur l’IA et la 3D pour les puces avancées

Selon le PDG de Synopsys, pionnier en matière d’outils de conception, l’IA, en stimulant le développement de conceptions multi-pièces, sera la clé de la réalisation de composants à mille milliards de transistors.

« Nous voyons trois grands moteurs de croissance pour l’industrie, a déclaré Sassine Ghazi, qui a succédé en janvier dernier à Aart de Geus, le PDG fondateur de Synopsys.

« L’accélération rapide de l’IA entraîne une amélioration massive de la productivité, non seulement dans notre espace, mais aussi dans de nombreux marchés finaux. Ensuite, il y a la prolifération du silicium. Ce qui va alimenter les progrès de l’IA, c’est le silicium », a-t-il déclaré lors de la réunion du Synopsys User Group (SNUG), qui célèbre cette année son 35e anniversaire.

« Le troisième grand facteur est l’importance croissante des systèmes définis par logiciel », a-t-il déclaré. « Il s’agit de l’interaction entre le silicium et le système afin d’obtenir le meilleur résultat possible pour les différentes charges de travail exécutées sur le silicium.

« Pour relever les défis qui vont de l’architecture du système à la conception du silicium, il faut une nouvelle approche et nous ne pouvons pas le faire seuls.

- Synopsys rachète Ansys pour 35 milliards de dollars de simulation et de jumeaux numériques

- Synopsys ajoute l’IA générative à ses outils de conception

C’est la raison d’être du projet d’acquisition d’Ansys pour 35 milliards de dollars, en particulier pour ajouter la modélisation physique et la technologie des jumeaux numériques à la plateforme de développement virtuel de Synopsys.

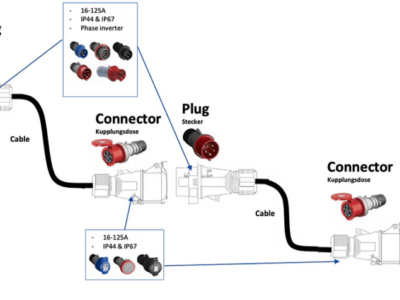

Dans le cadre de cette évolution, Synopsys présente 3DSO.ai, un nouvel outil piloté par l’IA qui est intégré nativement à Synopsys 3DIC Compiler pour fournir une plateforme unifiée d’exploration jusqu’àusign-off et qui est alimenté par des moteurs d’analyse rapides et intégrés. 3DSO.ai offre une optimisation de l’intégrité des signaux, de l’intégrité thermique et de la conception des réseaux d’alimentation pour la conception de chiplets et de multidie tels que le GPU Blackwell de Nvidia qui est composé de deux Dies (puces) sur un substrat avec une architecture de mémoire cohérente….

Synopsys 3DSO.ai est maintenant disponible pour les premiers utilisateurs tels que Nvidia et Intel.

- Intel se prépare à l’ère du trillion de transistors

- Synopsys achète Intrinsic-ID pour la sécurité des PUF

M. Ghazi a également présenté un outil d’exploration précoce de l’architecture des systèmes multi-filières, Synopsys Platform Architect – Multi-Die, qui accélère les délais de conception pour l’analyse des performances et de la puissance des conceptions de puces 3D, tout en tenant compte des interdépendances entre les différentes filières. Il permet aux architectes de systèmes d’automatiser la modélisation, la simulation et l’analyse pour prendre des décisions précoces en matière de partitionnement, et aide les clients à éviter les changements coûteux et les reprises en fin de processus.

En outre, il a souligné l’importance des solutions multi-pièces, en mettant en avant Pike Creek d’Intel, la première connexion UCIe au monde prouvée sur silicium, fruit d’une collaboration entre Intel, TSMC et Synopsys.

- Première puce chiplet de test hétérogène UCIe

- Nvidia présente le GPU Blackwell comme le point de départ d’une toute nouvelle technologie.

La puce, fruit d’une collaboration entre Intel, TSMC et Synopsys, comprend une puce UCIe IP d’Intel construite sur le nœud de traitement Intel 3 et une puce UCIe IP de Synopsys construite sur le processus N3E de TSMC. M. Ghazi a déclaré : « C’est l’avenir de l’industrie des semiconducteurs : de multiples fabs, de multiples ensembles d’IP UCIe standard et des solutions de packaging EDA modernes ».

Synopsys a également lancé la dernière version de ses systèmes de prototypage et d’émulation sur la voie des dispositifs à trillion de transistors. « Le HAPS 100 12 a une capacité accrue de 3x et une configuration réduite, et peut exécuter l’interface IP à 400 MHz », a déclaré Ghazi, « et nous avons deux hyperscalers utilisant le HAPS 100 12. Le Zebu EP2 (montré ci-dessus) est construit sur le HAPS 100 12 avec 5,6 milliards de portes dans le système d’émulation et de prototypage ».

Jensen Huang, PDG de Nvidia, qui a utilisé les outils de Synopsys dès le début en 1992, a également parlé au SNUG des changements induits par l’IA. « C’est la première fois en 60 ans que l’informatique est réinventée et la manière dont nous la construisons changera profondément au cours de la prochaine décennie », a-t-il déclaré.

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News