PCIe 8.0 vise les 256GT/s pour l’IA

Le groupe d’intérêt spécial (SIG) PCI vise des vitesses de 256GTransactions/s avec PCI Express (PCIe) 8.0 afin de fournir des liens plus rapides entre les puces pour l’IA.

Parallèlement, le consortium Universal Chiplet Interconnect Express (UCIe) a annoncé UCIe 3.0.

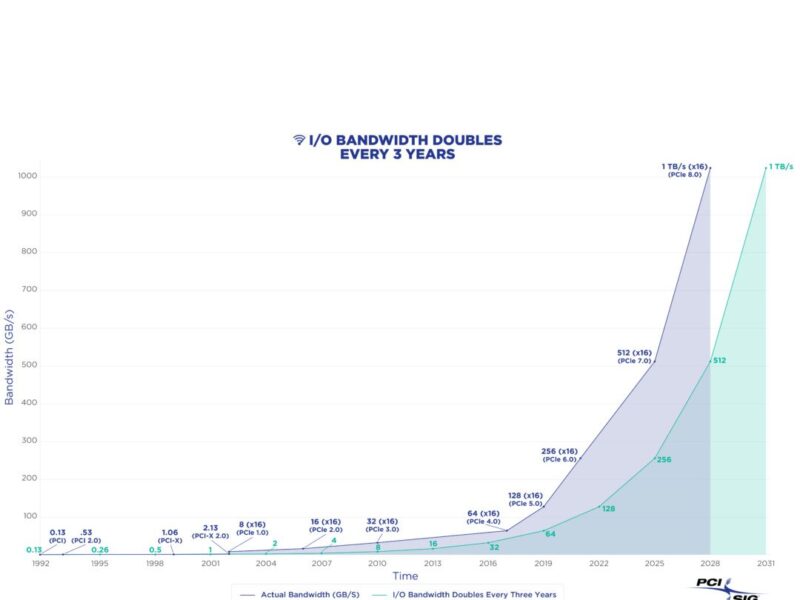

La spécification PCIe 8.0 doublera les données de la spécification PCIe 7.0 et sera disponible d’ici 2028.

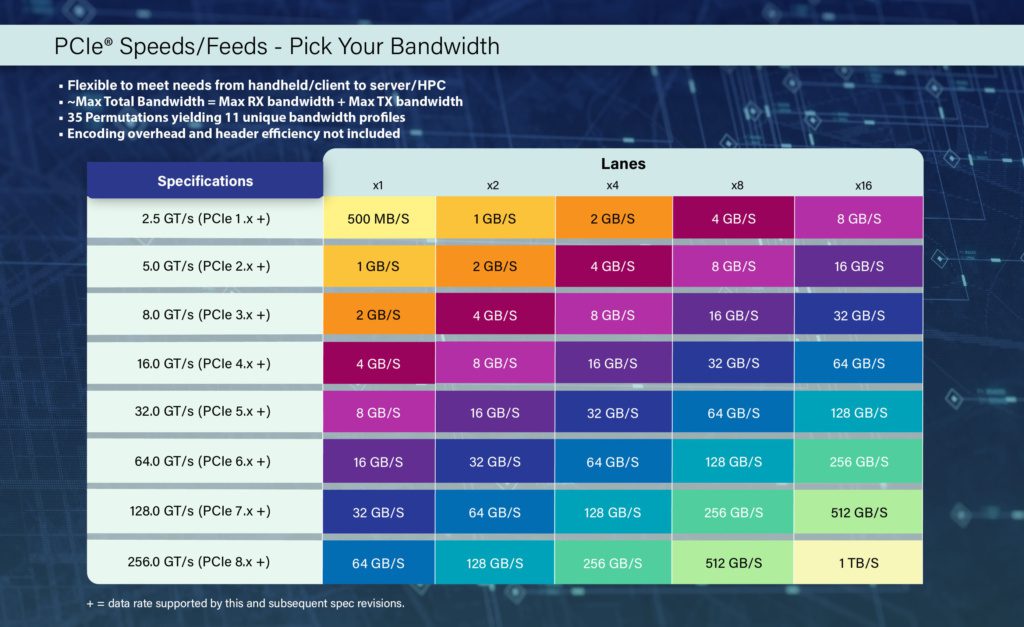

Les groupes de travail techniques du PCI-SIG développeront la spécification PCIe 8.0 avec un débit binaire brut de 256,0 GT/s qui permet d’atteindre 1 TB/s de manière bidirectionnelle dans une configuration x16. Cela nécessitera probablement une nouvelle technologie de connecteur et de nouvelles techniques pour réduire la consommation d’énergie.

- PCIe 7.0 et interconnexion optique pour l’IA et les liaisons avec les centres de données

- Synopsys lance une IP PCIe 7.0 de bout en bout

« Après la publication cette année de la spécification PCIe 7.0, la spécification PCIe 8.0 doublera le débit de données à 256 GT/s, maintenant notre tradition de doubler la bande passante tous les trois ans pour soutenir les applications de nouvelle génération », a déclaré Al Yanes, président du PCI-SIG et président du conseil d’administration. « Avec l’augmentation du débit de données requis dans l’IA et d’autres applications, il y a toujours une forte demande de haute performance. La technologie PCIe continuera à fournir une interconnexion d’E/S économique, à large bande passante et à faible latence pour répondre aux besoins de l’industrie. »

Vitesses PCIe Source : PCI-SIG

« Comme l’intelligence artificielle et d’autres applications à forte intensité de données continuent à évoluer rapidement, la demande de technologie PCIe sera soutenue à long terme en raison de sa bande passante élevée, de son évolutivité et de son efficacité énergétique », a déclaré Reece Hayden, analyste principal chez ABI Research. « Les réseaux de centres de données se préparent déjà à mettre en œuvre la technologie PCIe 6.0 et montrent un grand intérêt pour la spécification PCIe 7.0. L’introduction de la spécification PCIe 8.0 garantit que les exigences de l’industrie en matière de bande passante seront prises en charge à l’avenir.

La spécification PCIe 8.0 vise à soutenir les applications émergentes telles que l’intelligence artificielle/l’apprentissage machine, les réseaux à haut débit, l’informatique de pointe et l’informatique quantique, ainsi que les marchés à forte intensité de données tels que l’automobile, les centres de données à grande échelle, l’informatique à haute performance (HPC) et le secteur militaire/aérospatial.

PCI Express est un protocole clé pour le consortium Universal Chiplet Interconnect Express (UCIe) qui a également annoncé UCIe 3.0.

- L’IP UCIe 2nm prend en charge des données de puce à puce à 36 Gb/s

- La première puce optique CMOS UCIe atteint 8Tbit/s

La version 3.0 de la norme ouverte pour les interconnexions entre les puces à l’intérieur d’un boîtier double le débit de données avec la prise en charge des transferts à 48 GT/s et 64 GT/s, ainsi que des mises à jour architecturales incrémentielles pour répondre à la demande croissante de l’industrie pour des solutions interopérables à grande vitesse pour les puces.

La spécification UCIe 3.0 introduit également des améliorations telles que le recalibrage en cours d’exécution pour une meilleure efficacité énergétique grâce à l’ajustement de la liaison pendant le fonctionnement en réutilisant les états d’initialisation. Elle comprend également une bande latérale étendue qui prend en charge des configurations multi-puces plus flexibles avec des liens d’une longueur maximale de 100 mm.

La prise en charge des protocoles de transmission continue par le biais de mappages permet un flux de données ininterrompu en mode brut pour de nouvelles applications telles que la connectivité entre les puces SoC et DSP.

Le téléchargement précoce de logiciels avec un protocole de transport de gestion normalisé (MTP) et les paquets à bande latérale prioritaire augmentent la réactivité et la fiabilité du système. Il s’agit de fonctions de gérabilité optionnelles que les concepteurs peuvent mettre en œuvre s’ils choisissent une signalisation déterministe et à faible latence pour les événements système sensibles au temps.

« L’UCIe 3.0 représente une étape cruciale pour l’industrie des puces, car elle offre la vitesse, l’efficacité et la facilité de gestion nécessaires à la mise à l’échelle des conceptions multi-puces », a déclaré Cheolmin Park, président du consortium UCIe et vice-président de Samsung Electro-Mechanics. « Avec des débits de données accrus et des capacités de gestion étendues, la prochaine génération de technologie UCIe permettra aux développeurs de créer des solutions SiP plus flexibles, interopérables et performantes, alors que nous travaillons tous ensemble à la construction d’un écosystème de chiplets véritablement ouvert et interopérable. »

La spécification UCIe 3.0 est disponible sur demande à l’adresse www.uciexpress.org/specifications.

www.pcisig.com ; www.synopsys.com ; www.uciexpress.org/specifications

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News