Un filtre et un circuit de protection pour augmenter l’immunité au bruit du bus I²C

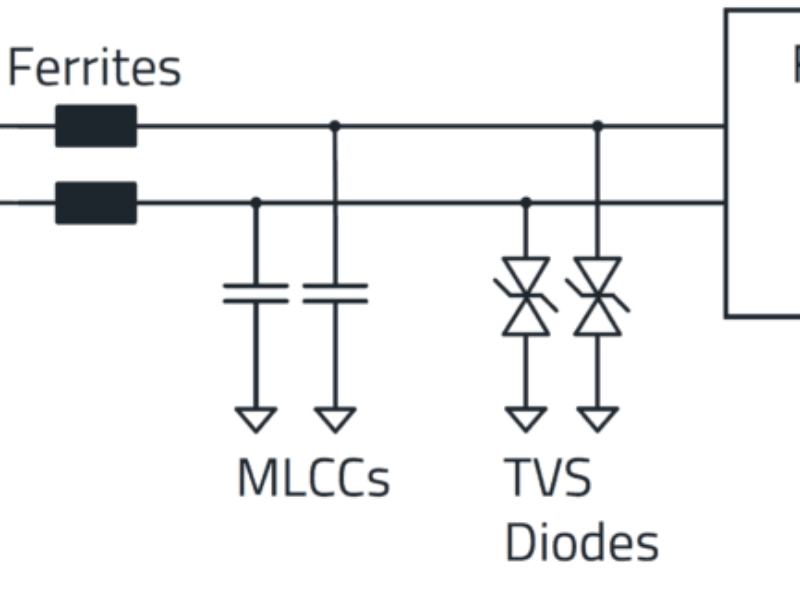

Würth Elektronik a publié une nouvelle note d’application : « ANP121 – Filtre et protection contre les surtensions pour bus I²C ».Dans cette nouvelle note, le fournisseur de composants électroniques et électromécaniques apporte une aide précieuse aux développeurs qui utilisent un bus I²C (Inter-Integrated Circuit Bus) dans des scénarios inter-carte. Une extension de l’interface via des connecteurs ou des câbles peut toutefois rendre le bus I²C sensible aux interférences externes telles que les décharges électrostatiques (ESD), les rafales et les radiofréquences rayonnées. L’objectif de cette note d’application est de présenter un filtre et un circuit de protection appropriés qui augmentent l’immunité au bruit du bus I²C sans compromettre la qualité du signal des lignes de données et d’horloge. Configuration de test avec FeatherWing Pour vérifier la simulation, des mesures supplémentaires ont été effectuées sur un kit SensorBLE FeatherWing de Würth Elektronik. Ce kit se compose d’une carte maîtresse avec un microcontrôleur et de deux autres cartes équipées d’un module Bluetooth WE et d’un système FeatherWing avec des capteurs WE (accélération à 3 axes, température, humidité, pression). La carte maîtresse communique avec les deux autres cartes via le bus I²C à un débit maximum de 400 kBit/s. Un câble de données de 20 cm de long a été utilisé pour connecter la carte du capteur au reste du bus I²C. Une capacité parasite de 400 pF par rapport à la masse a été simulée en utilisant des MLCC. La simulation et la mesure ont montré que les ferrites multicouches CMS en combinaison avec des diodes de protection ESD n’ont pratiquement aucun effet sur le signal de données (SDA) et le signal d’horloge (SCL) du bus I²C, mais qu’elles améliorent plutôt l’immunité au bruit du bus I²C. |

Suivre ECInews sur Google news

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News