L’IA au service des capteurs d’images CMOS avec l intégration à trois couches

Le CEA-Leti, a mis au point un procédé permettant de combiner le collage hybride et les trous d’interconnexion à haute densité pour ajouter de l’intelligence artificielle aux capteurs d’images CMOS.

L’intégration de l’IA par le CEA-Leti permet une nouvelle génération de capteurs d’images CMOS (CIS) capables d’exploiter toutes les données d’image pour percevoir une scène, comprendre la situation et intervenir.

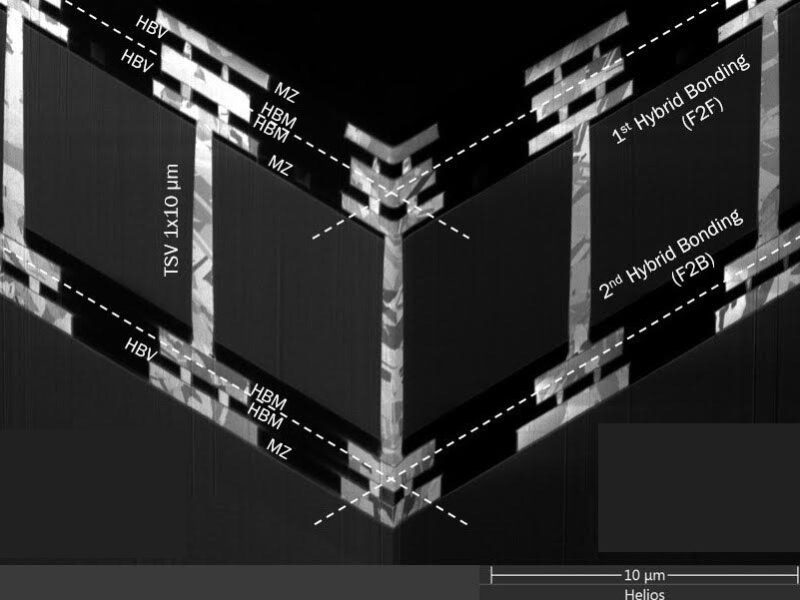

Le projet a développé un véhicule de test à trois couches comportant deux interfaces de liaison hybride Cu-Cu intégrées, face à face (F2F) et face à dos (F2B), et avec une tranche contenant des TSV haute densité.

Les détails ont été présentés cette semaine lors de la conférence ECTC 2024 à Denver et s’appuient sur des travaux antérieurs sur l’empilement de trois tranches de silicium de 300 mm.

Une demande croissante de capteur intelligents

La demande de capteurs intelligents augmente rapidement en raison de leurs capacités d’imagerie haute performance dans les smartphones, les appareils photo numériques, les automobiles et les appareils médicaux. Cette demande d’amélioration de la qualité d’image et des fonctionnalités améliorées par l’IA intégrée a posé aux fabricants le défi d’améliorer les performances des capteurs sans augmenter la taille de l’appareil.

Architecture 3d

Renan Bouis, chercheur au CEA-Leti à Grenoble. a déclaré : « L’empilement de plusieurs puces pour créer des architectures 3D, telles que des imageurs à trois couches, a conduit à un changement de paradigme dans la conception des capteurs. La communication entre les différents niveaux nécessite des technologies d’interconnexion avancées, une exigence à laquelle la liaison hybride répond en raison de son pas très fin dans la plage micrométrique et même submicrométrique ».

Le via silicium haute densité (HD TSV) a une densité similaire qui permet la transmission du signal à travers les niveaux intermédiaires. Les deux technologies contribuent à la réduction de la longueur des câbles, un facteur essentiel pour améliorer les performances des architectures empilées en 3D.

« Ces articles présentent les briques technologiques clés nécessaires à la fabrication d’imageurs intelligents 3D multicouches, capables d’adresser de nouvelles applications nécessitant une IA embarquée », a déclaré Eric Ollier, chef de projet au CEA-Leti et directeur du programme Smart Imager de l’IRT Nanoelec. L’institut CEA-Leti est un partenaire majeur de l’IRT Nanoelec.

« La combinaison de la liaison hybride avec les HD TSV dans les capteurs d’images CMOS pourrait faciliter l’intégration de divers composants, tels que des réseaux de capteurs d’images, des circuits de traitement du signal et des éléments de mémoire, avec une précision et une compacité inégalées », a déclaré le chercheur Stéphane Nicolas.

Stéphane Nicolas continu : »Le véhicule de test constitue une étape clé car il démontre à la fois la faisabilité de chaque brique technologique et également la faisabilité du flux du processus d’intégration. « Ce projet ouvre la voie à la démonstration d’un capteur d’image CMOS intelligent à trois couches entièrement fonctionnel, doté d’une IA de pointe capable de répondre à des applications de segmentation sémantique et de détection d’objets hautes performances ».

L’année dernière, les scientifiques du CEA-Leti ont présenté un véhicule d’essai à deux couches combinant un HD TSV de 10 microns de haut et 1 micron de diamètre et une technologie de liaison hybride hautement contrôlée, tous deux assemblés en configuration F2B. Les travaux récents ont ensuite raccourci le HD TSV à six microns de hauteur, ce qui a conduit au développement d’un véhicule d’essai à deux couches présentant des performances électriques à faible dispersion et permettant une fabrication plus simple.

« Notre HD TSV en cuivre de 1 x 6 microns offre une résistance électrique et des performances d’isolation améliorées par rapport à notre HD TSV de 1 x 10 microns, grâce à un processus d’amincissement optimisé qui nous a permis de réduire l’épaisseur du substrat avec une bonne uniformité, » a déclaré le chercheur Stéphan Borel.

« Cette hauteur réduite a entraîné une diminution de 40 % de la résistance électrique, proportionnellement à la réduction de la longueur. La réduction simultanée du rapport d’aspect a augmenté la couverture des marches du revêtement d’isolation, conduisant à une meilleure tenue à la tension », a-t-il ajouté.

« Avec ces résultats, le CEA-Leti est désormais clairement identifié comme un leader mondial dans ce nouveau domaine dédié à la préparation de la prochaine génération d’imageurs intelligents », a déclaré Ollier. « Ces nouveaux imageurs intelligents multicouches 3D avec Edge AI implémentés dans le capteur lui-même constitueront une véritable avancée dans le domaine de l’imagerie, car Edge AI augmentera les performances de l’imageur et permettra de nombreuses nouvelles applications. »

www.leti-cea.com ; https://irtnanoelec.fr/actualites/smart-imager-from-imaging-to-vision-sensing/

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News