Le CEA-Leti améliore les performances du FD-SOI de 450%

gtag(‘js’, new Date()); gtag(‘config’, ‘UA-160857065-1’);

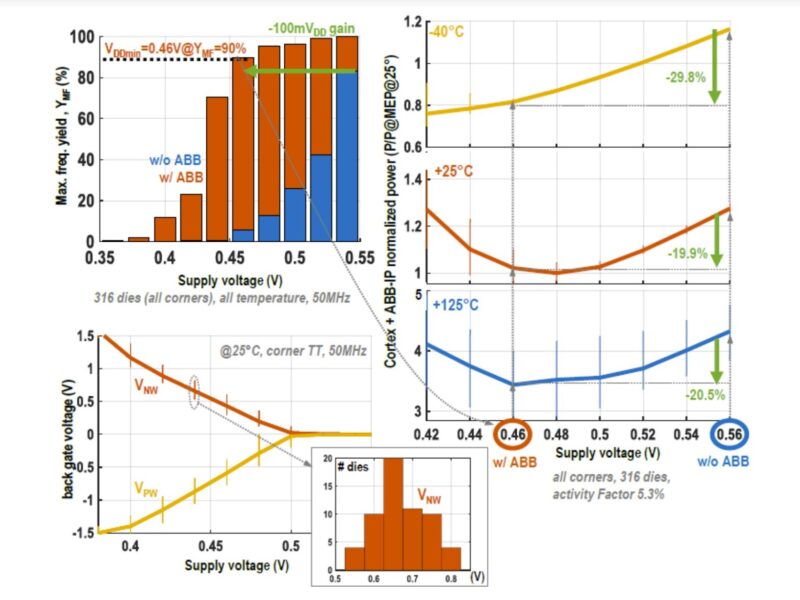

Le CEA-Leti et Dolphin Design ont développé une architecture de contre-polarisation adaptative (ABB, pour adaptive back-biasing) pour les puces FD-SOI (silicium sur isolant) entièrement appauvri qui peuvent être intégrées de manière transparente dans un flux de conception industrielle. Cela active un régulateur minuscule qui fournit un contrôle stable de l’ABB dans la puce.

FD-SOI permet la polarisation du corps du transistor qui agit comme une grille arrière. Contrairement à la technologie conventionnelle, FD-SOI permet une large plage de tension de la polarisation du corps du transistor. Cela permet de compenser les variabilités du process, de tension et de température (PVT) en contrôlant la tension de seuil.

Par exemple, dans les opérations de commutation, lorsque le commutateur est activé, la polarisation du corps est modifiée pour réduire la résistance à l’état passant en réduisant la tension de seuil et en laissant passer plus de courant. Cela accélère le circuit. Dans l’état désactivé, la polarisation du corps est modifiée pour augmenter la résistance d’arrêt en augmentant la tension de seuil, réduisant par conséquent le courant de fuite. Cela permet aux concepteurs d’augmenter la fréquence de fonctionnement ou de réduire la puissance de fuite.

La nouvelle technique ABB permet également à une conception de maintenir une fréquence de fonctionnement donnée sur une large gamme de conditions de fonctionnement telles que la température, la variabilité de fabrication et la tension d’alimentation. Cela augmente les performances et le rendement des conceptions dans la technologie de processus FD-SOI 22 nm actuelle.

«Le développement de l’ABB est une percée pour la technologie FD-SOI car il montre pour la première fois des résultats illustrant l’amélioration des performances du circuit après l’utilisation de l’ABB, et il contribuera à augmenter les performances et les rendements dans les conceptions FD-SOI», a déclaré Gaël Pillonnet, scientifique du CEA-Leti et auteur de l’article de l’ISSCC. Le régulateur ABB ne mesure que 0,021 mm² dans le process 22 nm FD-SOI.

Le bloc IP ABB est commercialisé par la maison de design française Dolphin Design sur la base de la preuve de concept du CEA-Leti.

à suivre: Commercialisation du bloc IP de conception FD-SOI

«Les performances de notre IP ABB sont à la pointe de la technologie et montrent la compensation des variations à travers les conditions de process-tension-température (PVT) sur un nombre représentatif d’échantillons, permettant l’utilisation de cette solution dans les produits industriels», a déclaré Andrea Bonzo , Responsable de programme IP chez Dolphin Design.

«Les efforts précédents dans cette technique n’ont rapporté qu’un nombre limité de puces fonctionnant comme prévu. Grâce à notre technique, un grand nombre de puces fonctionnent correctement. Notre ABB est polyvalent et peut être utilisé pour piloter une grande zone numérique sans aucune limitation pour toute technologie FD-SOI. »

Avec cette nouvelle architecture, la zone ABB est relativement petite par rapport à la conception de l’application, et à la fois en zone et en puissance, elle permet à la conception de l’application de maintenir sa fréquence cible avec une surcharge relativement faible.

Lire aussi:

Nokia va diriger le projet Hexa-X de l’UE sur la 6G

Objectif 6G dans la bande des 140 GHz pour le CEA-Leti

L’Europe lance son grand projet 6G Hexa-X

SiPearl fabrique sa puce 6nm HPC chez TSMC

Related FD-SOI articles

- SOI CONSORTIUM COMBINES WITH SEMI

- LOW POWER BREAKTHROUGH FOR EDGE AI CHIPS

- GLOBALFOUNDRIES EXTENDS 22nm PROCESS, HOLDS 12nm

- ARTERIS IP TO ACQUIRE FRENCH SoC DESIGN TEAM

Other articles on eeNews Europe

- NXP, Infineon plants hit by power outage in Texas storm

- BritishVolt gigafactory founder tries again in Italy

- Objections grow to Nvidia-ARM deal

- Intel brings Ignite startup scheme to Europe

- Europe needs to wake from its 30-year semiconductor sleep

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News