À la poursuite de puces quantiques intégrées, grâce au FD-SOI

Une startup quantique issue du CEA-Leti en France vise à utiliser les process de fabrication de silicium existants avec le FD SOI pour construire des puces quantiques intégrées supraconductrices à grande échelle et au delà, des systèmes informatiques.

Siquance a été créé grâce aux recherches effectuées au Leti par Maud Vinet (ci-dessus) et deux collègues chercheurs pour exploiter l’écosystème du silicium autour de Grenoble, en particulier l’expertise en matière de silicium sur isolant entièrement appauvri (FD-SOI), et le passage aux géométries 10nm et 7nm de la prochaine génération avec la ligne pilote en cours de construction au Leti.

La startup étudie donc en détail l’architecture requise pour les puces intégrées avec l’électronique de contrôle et les réseaux de qubits de spin sur le même composant qui peut être utilisé dans un cryostat surper froid.

« Il y a six mois, nous avons lancé une startup pour construire un ordinateur quantique utilisant du silicium, sur la base de 15 années de recherche », a-t-elle déclaré. « En tant que startup, nous avons maintenant 10 employés et nous construisons une équipe avec une expertise en physique et en technologie.

« L’enjeu est de taille, car si nous parvenons à faire de l’informatique quantique une réalité, cela aura un impact sur toutes les industries qui utilisent aujourd’hui l’informatique à haute performance (HPC). Mais cela ne sera possible que si nous parvenons à fabriquer un grand nombre de qubits de haute qualité ».

Qubits de spin

Jusqu’à présent, les technologies prototypes ne comportaient pas beaucoup de qubits et n’étaient pas de grande qualité, explique-t-elle. C’est ce qui pousse à la correction d’erreurs, à la création d’un qubit logique à partir de milliers de composants physiques.

- Intel présente une puce quantique CMOS de 12 bits produite en masse

- Intel augmente les rendements des points quantiques EUV

- IBM développe un superordinateur centré sur les quanta de 100 000 qubits

- Le Leti détaille le passage au procédé FD-SOI 10nm, 7nm en Europe

« Pour être utiles, nous devons dépasser les 100 000 qubits et nous ne savons pas encore comment y parvenir », a-t-elle déclaré. « C’est ce que Siquance promet, à savoir trouver la voie vers l’informatique quantique à grande échelle, et le silicium y contribuera.

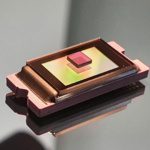

« Le silicium permet de concevoir de bons qubits, d’environ 100nm2, qui sont de haute qualité avec une cohérence de l’ordre de la milliseconde et des vitesses de l’ordre de la microseconde », a-t-elle déclaré. « C’est difficile à faire. Les transistors et les qubits sont très différents et il y a définitivement un fossé entre les transistors et les qubits. Les transistors ont été optimisés pour délivrer des courants importants à température ambiante, alors que les qubits n’ont qu’une seule charge et sont très sensibles à leur environnement ».

« Dans les laboratoires de physique, il existe de nombreux systèmes permettant de mettre en œuvre des qubits de spin en silicium. Après la première démonstration de quelques qubits, comment pouvons-nous répéter cela avec des qubits de haute performance partout ? En utilisant le FD-SOI, nous pouvons combler le fossé entre les transistors et les qubits, ce qui nous permet de concevoir des réseaux de qubits avec l’électronique de contrôle sur le même substrat et de les conditionner de manière à ce qu’ils puissent entrer dans le cryostat. L’avantage est que les qubits se trouvent dans une puce de 1 cm2 et qu’au fur et à mesure que nous évoluons, nous pouvons retirer la carte du cryostat et en mettre une nouvelle.

« Le FD-SOI présente un grand avantage : en polarisant la grille arrière, nous pouvons éloigner les charges des interfaces, ce qui les rend moins sensibles au bruit. Nous avons ainsi réduit le bruit de charge d’un facteur dix. Nous avons développé la preuve de concept en 2016, et avons plus de 40 brevets déposés pour la startup.

Depuis lors, la qualité des qubits de spin a été améliorée en utilisant à la fois des trous et des électrons, et l’avantage est que le temps de cohérence plus élevé permet aux qubits de se coupler avec un qubit photonique sur une distance de 2 à 3 mm, au lieu d’une séparation de quelques nanomètres.

Puces quantiques intégrées

« Le principal défi consiste à contrôler la dissipation thermique de l’électronique de commande et le FD-SOI est à nouveau très intéressant à cet égard », a déclaré M. Vinet.

« Nous savons que l’industrie a besoin de données statistiques à basse température, qui constituent la partie manquante de la chaîne complète, et nous travaillons sur les signaux de contrôle et les protocoles de contrôle des qubits afin d’augmenter la fidélité à 99,99 % ce qui permet d’obtenir un temps de cohérence record. »

En collaboration avec STMicroelectronics et Global Foundries, la startup prévoit de disposer d’un système en boîtier (SiP) en 2025, combinant un réseau de qubits avec la logique du contrôleur. Ce contrôleur sera intégré à un réseau 2D de qubits sur une seule puce d’ici 2027. Cela conduira à des puces quantiques multicœurs avec des réseaux de qubits en 2D qui pourront fonctionner dans les locaux des clients, explique M. Vinet.

- Un projet de 6,5 millions de livres sterling vise à développer une propriété intellectuelle CMOS cryogénique pour l’informatique quantique

- SureCore se développe dans la logique de contrôle pour l’informatique quantique

La consommation d’énergie est également essentielle, car l’ordinateur quantique fonctionnera à quelques millikelvins.

« Nous prêtons déjà attention à la consommation d’énergie et en augmentant la qualité des qubits, nous pouvons réduire l’énergie car il faut moins d’électronique de contrôle. Il y a un compromis à faire et c’est quelque chose que nous examinons très attentivement », a-t-elle déclaré.

L’étape suivante consiste à évaluer les éléments constitutifs des puces et de l’architecture. « Il est très intéressant d’avoir l’amplification analogique avec l’amplificateur à transimpédance (TIA) près des qubits. Ensuite, nous mesurons les blocs de construction, les mémoires, les communications, pour voir quelle quantité d’électronique nous pouvons intégrer à proximité des qubits », a-t-elle déclaré.

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News