Lasers quantum dots intégrés sur chiplets de silicium

Des chercheurs américains ont réussi à intégrer des lasers quantum dots (QD) à l’arséniure d’indium de manière monolithique sur des puces photoniques en silicium.

L’intégration de lasers dans le silicium est une technique clé pour réduire la consommation d’énergie des puces d’intelligence artificielle dans les centres de données, à mesure que les vitesses d’interconnexion augmentent. Nvidia, par exemple, travaille avec TSMC sur un système photonique en silicium copackagé (CPO) d’une performance de 1,6 Tbit/s basé sur des micro-résonateurs en anneau pour les chiplets.

- Un quantum de couplage

- Interconnexion optique térabitaire de Celestial AI

- Puce photonique 3D avec une bande passante de 114Tbit/s

Cependant, l’intégration des lasers constitue un défi majeur car le silicium et les matériaux III-V présentent des disparités inhérentes en termes de constante de réseau et de coefficient de dilatation thermique. Celles-ci entraînent des dislocations qui dégradent les performances des composants.

Rosalyn Koscica, de l’université de Californie à Santa Barbara, et son équipe ont combiné trois concepts clés : des poches de silicium en retrait pour la croissance des matériaux III-V, un processus d’épitaxie en deux étapes utilisant à la fois le MOCVD et le MBE, et une approche de remplissage de l’espace des facettes en polymère qui minimise la divergence du faisceau optique dans l’espace. Cela permet d’intégrer de manière monolithique des lasers quantum dotd à l’arséniure d’indium (InAs) sur des chiplets photoniques en silicium. Ces lasers quantum dots utilisant la bande O présentent une dispersion moindre que d’autres types de lasers tels que les VCSEL, ainsi qu’une plus grande stabilité thermique.

« Nos lasers QD intégrés ont démontré un fonctionnement à haute température jusqu’à 105 °C et une durée de vie de 6,2 ans à une température de 35 °C », explique le Dr Koscica.

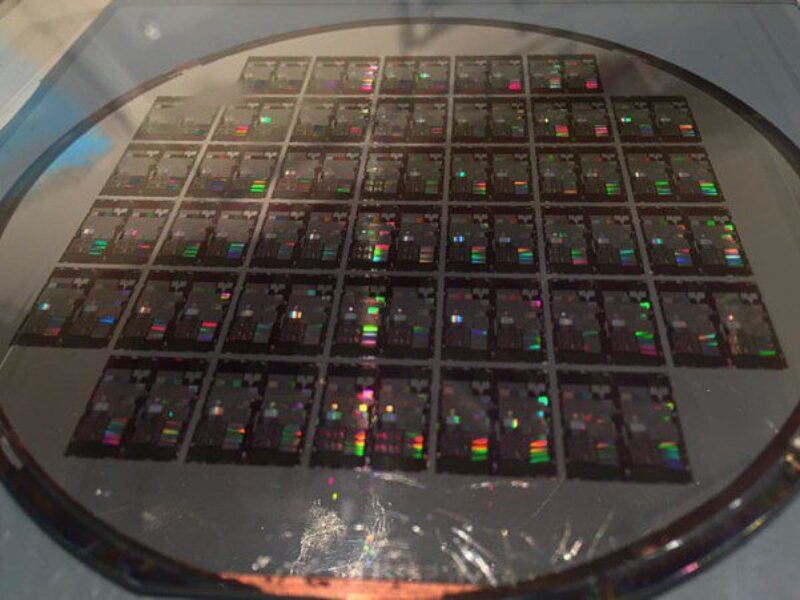

Plaquettes SOI de 300 mm

Le processus peut être appliqué dans une ligne CMOS de silicium sur isolant (SOI) sur des plaquettes de 300 mm pour plus d’efficacité. Les premiers composants photoniques au silicium sont fabriqués sur une tranche de silicium sur isolant (SOI) de 300 mm dans la fonderie d’AIM Photonics.

Le processus de 300 mm crée des composants photoniques en silicium intégrés dans une couche de revêtement de SiO2 de 4 μm qui couvre l’ensemble de la plaquette avec des anneaux de microrésonateurs en silicium traités en fonderie et des guides d’ondes en nitrure de silicium (SiN). Environ 5 % de la surface de SiO2 est lithographiée et gravée pour ouvrir des poches rectangulaires avec une base de Si en retrait pour la croissance épitaxiale de III-V.

La profondeur de l’évidement Si est conçue compte tenu de l’empilement épi prévu pour un alignement optimal entre les modes optiques du laser et du coupleur d’entrée du guide d’ondes. Les poches mesurent 50 μm par 4 μm pour maximiser les performances du composant tout en conservant l’empreinte étroite requise pour l’intégration à haute densité.

Lors des essais, les chiplets dotés de lasers intégrés de manière monolithique ont montré une perte de couplage suffisamment faible, fonctionnant efficacement sur une seule longueur d’onde en bande O au sein des chiplets. La longueur d’onde de la bande O est souhaitable car elle permet la transmission de signaux dans des dispositifs photoniques à faible dispersion. Les lasers à fréquence unique sont réalisés à l’aide de résonateurs annulaires en silicium ou de réflecteurs de Bragg distribués en nitrure de silicium.

La technique d’intégration proposée peut être appliquée à une variété de circuits intégrés photoniques.

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News