Astrus, le moteur IA révolutionnant les puces analogiques

La start-up Astrus Inc. (Toronto, Canada) a développé un moteur d’intelligence artificielle pour le layout des circuits analogiques qui, selon elle, peut accélérer la conception des puces de plusieurs ordres de grandeur.

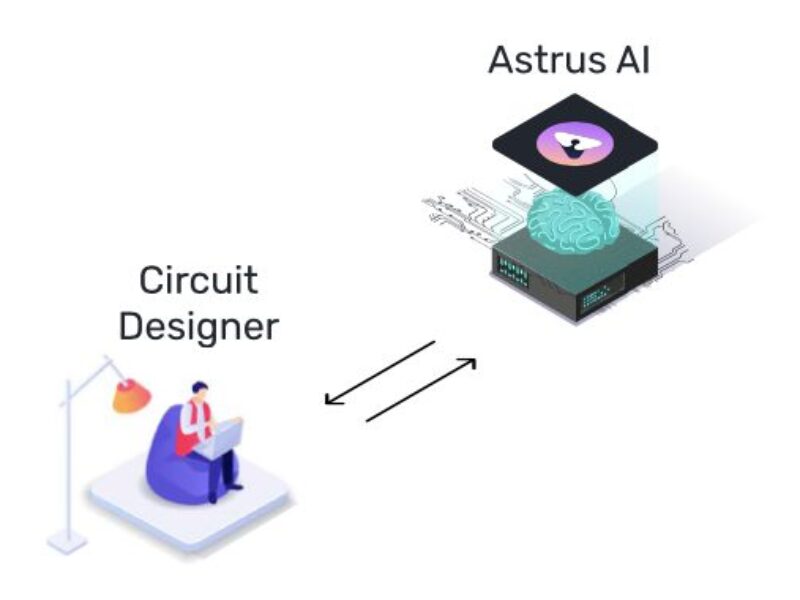

Astrus prévoit d’automatiser le layout des circuits intégrés analogiques à l’aide d’une IA d’apprentissage automatique en profondeur. Traditionnellement, la configuration des circuits intégrés analogiques est un processus manuel qui implique plusieurs itérations entre l’ingénieur de développement du circuit et l’ingénieur de configuration pour optimiser la surface de silicium et les performances. Astrus a l’intention de permettre plusieurs itérations par jour avec son moteur d’IA remplaçant l’ingénieur de layout.

Après un apprentissage approfondi, Astrus aura une compréhension nuancée de l’art du layout de circuits analogiques, affirme la société. La technologie fonctionne avec n’importe quel circuit, mais les points de départ évidents incluent les amplis opérationnels, les ADC SAR, les PLL, les onduleurs et les LDO, a-t-il ajouté.

Khosla investit 100 000 $Khosla invests $100,000

La société a été fondée par Brad Moon (CEO) et Zeyi Wang (CTO) en 2022 et a reçu 275 000 USD en financement de pré-amorçage de Khosla Ventures, RISC Capital et le fonds 1517. Moon est diplômé en 2017 de l’Université de l’Alberta, où il s’est spécialisé dans la conception de circuits intégrés analogiques. Wang était assistant de recherche à la même université où il a travaillé sur l’IA et le renforcement de l’apprentissage en profondeur.

Astrus est à un stade précoce de son développement et n’a pas encore de produit, mais il a un prototype de démonstration qui a reçu des commentaires positifs de la part des utilisateurs. La société envisage de pouvoir vendre des licences d’outils pour prendre en charge jusqu’à 60 000 ingénieurs de circuits intégrés analogiques dans le monde moyennant des frais annuels de 40 000 USD ou plus par utilisateur.

La société a sa preuve de concept technique, mais déclare qu’elle souhaite maintenant utiliser son financement de pré-amorçage pour créer des layouts du monde réel qui battent les êtres humains en termes de vitesse et de qualité. Une fois ces résultats obtenus, la société prévoit de co-rédiger un livre blanc avec le partenaire qui serait de préférence une marque leader telle qu’Intel.

Après cela, un tour de table d’environ 5 millions de dollars US fournirait des fonds pour produire et itérer la technologie afin d’en faire un incontournable pour les ingénieurs de circuits analogiques. L’entreprise recrute actuellement des ingénieurs logiciels et en expérience utilisateur. Selon des rapports, Astrus est en pourparlers avec Intel sur l’utilisation pilote du logiciel de mise en page Astrus au sein de l’entreprise.

Related links and articles:

News articles:

Chiplet manufacturing gains interface bus upgrade, PHY generator

Rapid Silicon lets engineers use GPT for FPGA design

ChatGPT leaking Samsung chip secrets is iceberg’s tip

Microsoft announces multibillion investment in OpenAI

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News

Si vous avez apprécié cet article, vous aimerez les suivants : ne les manquez pas en vous abonnant à :

ECI sur Google News